ATEの記事

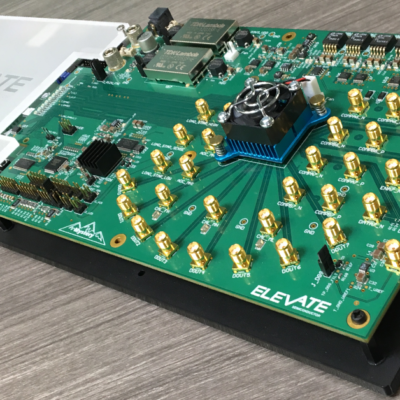

Elevate Semiconductor はさまざまな製品を提供しており、評価モジュール (EVM) は評価において極めて重要な役割を果たします。

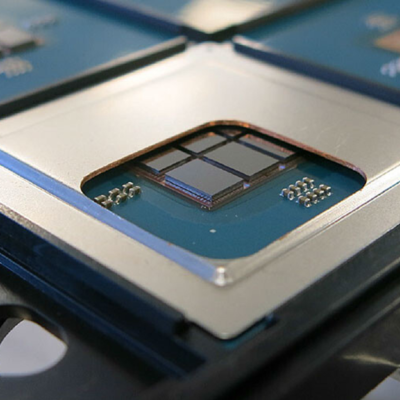

半導体チップレットのテストにおける複雑な課題への取り組み 半導体技術において、チップレットは、次のいずれかを実行できるモジュール式コンポーネントとして登場しました。

ElevATE の高速 IC 設計ディレクター、Anthony Turvey へのインタビュー インタビュアー: どのようにしてこの業界にたどり着いたのでしょうか?

Graphcore や NVIDIA の AI スーパー チップ GH200 などの著名なモデルなどの AI プロセッサは、恐るべき計算能力を発揮します。力を込めて…

Simon Leigh、Elevate エンジニアリング担当副社長 テストの複雑さが増すにつれ、ATE ベンダーは継続的に…

テストを成功させる: チップの裏にあるチップ。 ENGINEERING.COM 重要な ATE 業界は、かつてないほどの課題に直面していますが、企業は次のようなものです…

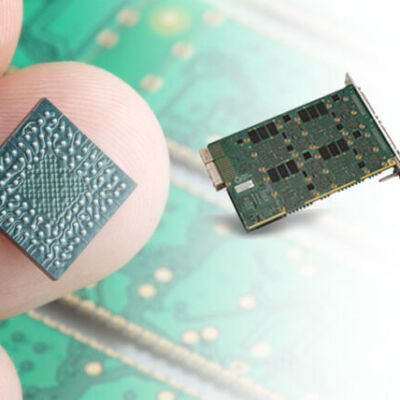

ATE デジタル システムは従来、シーケンサー、フォーマッタ、タイミング ジェネレーター、ピン エレクトロニクスで構成されていました。どのコンポーネントを使用するかについての決定…

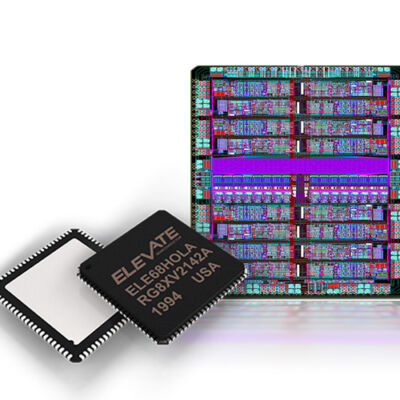

ピン エレクトロニクス (PE) 用の一般的な集積回路 (IC) ソリューションは、複数の半導体企業によって複数の異なるプロセスで提供されています。

MIPI 仕様とテスト ATE 記事 / By admin モバイル産業プロセッサ インターフェイス (MIPI®) 標準は、設計の業界仕様を定義します。

テクノロジーが進化し、人工知能、ディープラーニング、機械学習、自動車、IoT、ヘルスケアなどの次世代チップの需要が高まるにつれて…

デバイス電源 (DPS) 半導体は、幅広いテストに対応する柔軟な電圧および電流力測定機能を提供します。

ELEVATE: 統合テスト技術の世界リーダー 半導体テストの基本: 技術愛好家は、次の数値を示すムーアの法則を知っています…