ATEデジタルシステムは、伝統的にシーケンサー、フォーマッター、タイミングジェネレーター、 ピンエレクトロニクス。設計の各セクションに使用するコンポーネントの決定は、主にパフォーマンス仕様と必要なコストによって決まります。これらのコンポーネントは、ディスクリートの完全カスタムASIC、フィールドプログラマブルゲートアレイ、または市販の部品にまで及びます。

フィールドプログラマブルゲートアレイ(FPGA)は柔軟性を提供し、シーケンサーおよび低/中性能のATEデジタルサブシステムのタイミング/フォーマットに使用されています。

シーケンサーをFPGAに実装すると、ロジック、メモリ、または混合信号のテスト用にデジタルサブシステムをカスタマイズする柔軟性が提供されます。必要なFPGAクロッキングは通常、ターゲットFPGAの仕様の範囲内です。シーケンサーとパターン実行ステージは、通常、競合他社の製品と比較して各システムを独自のものにします。

形式とタイミングの機能は、通常、さまざまなATEプラットフォーム間で類似しています。違いは、サイクル間のエッジ配置の分解能と精度、およびチャネルのデスキューキャリブレーションに使用されるファインスキューコントロールにあります。多くの場合、ピンエレクトロニクスICでは細かいデスキュー制御が利用できます。

FPGAはタイミングとフォーマット機能に成功裏に使用されていますが、システムパフォーマンス要件が50-100Mhz以上のパターンレートに増加し、システムエッジの配置精度が1ns未満になると、FPGAはすぐに制限要因になります。 FPGA I / O構造のSERDESエンジンは100ps未満の分解能を提供できますが、エッジ間のタイミング配置にこの信頼性を実装すると、設計時間が増加し、設計者はより大きくてより高価なFPGAを選択する必要があります。

SERDESブロックの最も一般的な使用法は、PCIeなどのさまざまな通信プロトコル用です。FPGA設計ツールは、これらの機能を設計および特性評価するための優れたツールを提供します。これらのSERDESブロックを使用してタイミングセクションを設計する場合、設計者はしばしばロードブロッキングに遭遇し、FPGAベンダーから問題を解決するために利用できるツールは限られています。多くの場合、設計者はこれらのタイミング回路の実装と特性評価に予算の10倍のエンジニアリング時間を費やしています。典型的な問題には、チャネル間で一貫性のない直線性、許容可能なジッターより高い、実行から実行への設計のルーティングの困難さなどがあります。

設計者はチャネル数を増やすことを試みるので、より大きくてより高価なFPGAに移行する必要があります。これまで、設計者はより高速で大規模なFPGAを低コストで活用することができました。ただし、最近では、FPGA企業の焦点は、データセンターおよび人工知能市場に対応するための計算能力を高めることです。このようにコンピューティングエレメントを追加すると、コストが増加し、ATE設計者にとってのメリットが最小限またはマイナスになります。さらに、ATE市場に対応する古いデバイスのコストは、特に大きなデバイスの場合、劇的に上昇し始めています。これにより、FPGAだけで、より大きなFPGAを使用してより高いチャネルATEのコストを最大$50 /チャネルに押し上げました。

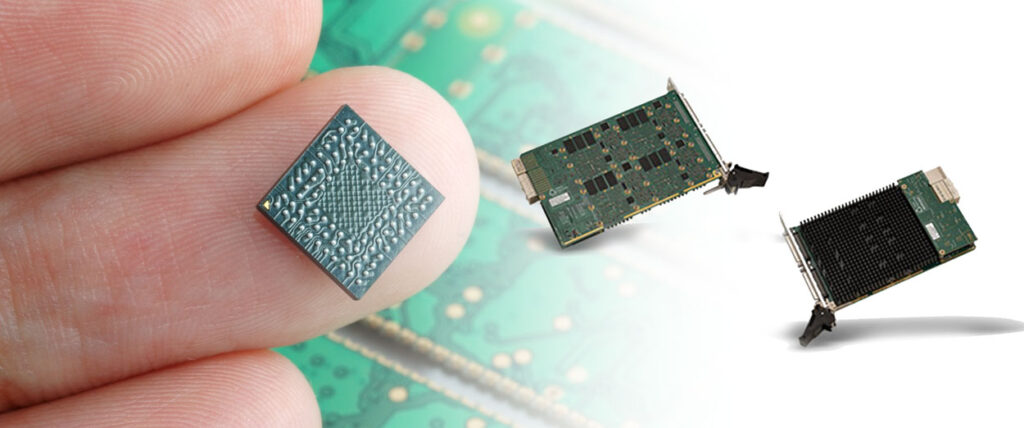

200 MHz以上のパターンレートでより高性能のATEを実現するには、カスタムまたは市販のフォーマットおよびタイミングジェネレーターICを使用する必要があります。その後、設計のシーケンサー部分に妥当なコストのFPGAを使用できます。

市販のタイミングジェネレーターを使用すると、小規模なATE企業がデジタルATE計測のパフォーマンスラダーを移行できます。これらのチップは、制約の厳しいFPGA I / Oを必要とせずに、高性能ピンドライバーにインターフェースするように設計されています。

ハイエンドのパフォーマンスを備えたタイミングチップを購入することで、設計、特性評価、テスト時間を短縮できるだけでなく、より高性能なデジタルATE仕様を提供しながら、チャネルあたりのコストを削減できます。タイミング精度はベンダーによって指定されており、システムテストでこれらのパラメーターの広範な特性評価や製造テストを行う必要はありません。

商用タイミングチップは最終的に節約します ATE会社 より高いエンドパフォーマンスへの道を提供しながら、開発コストと市場投入までの時間、およびシステムの全体的なコスト。