半導体チップレットテストにおける複雑な課題への取り組み

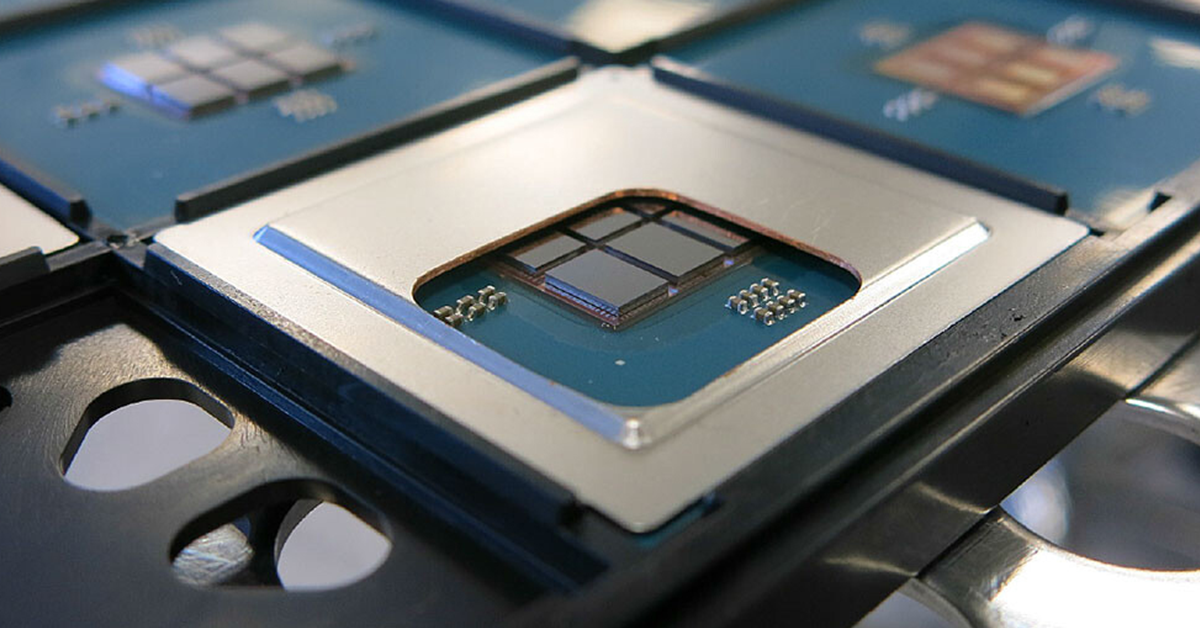

半導体技術では、チップレットは、単一の基板上で独立してまたは集合的に動作できるモジュール式コンポーネントとして登場しました。すべての機能を 1 つのユニットで管理するモノリシック チップとは異なり、チップレットは特定のタスクを個別の IC に割り当てることで設計を合理化します。このモジュール設計は、柔軟性、最適化されたパフォーマンスと効率を提供するだけでなく、この記事で説明するように、テストと検証に関して独特の課題ももたらします。

チップレットのテストは、チップレットの複雑さの増大、多くの場合プロセス技術の高密度化、およびパフォーマンスの向上への取り組みにより、困難な作業を伴います。プローバーは、チップレットを完全なソリューションにパッケージ化する前にチップレットをテストするために使用されます。チップレットが密集し、相互接続が複雑なため、プローバーがチップレットの機能とパフォーマンスを完全に評価するのは困難です。プロービング段階で包括的なテストが行われないということは、最終テストでの歩留まり低下にコストがかかることを意味します。その他の課題には、大量のテスト データの管理、複雑なインターフェイス プロトコルの操作、高速要件への対応などが含まれます。ただし、これらの課題に対処することは、最新の半導体の機能とパフォーマンスを確保するために非常に重要です。

自動テスト装置を使用したチップレットのテスト

自動テスト装置 (ATE) システムはプローバーに接続され、集積回路がパッケージングの準備ができているかどうかを確認します。通常、パッケージ化された IC は、デバイスをより包括的かつ迅速に検証するために、ATE のみの最終テストで再度テストされます。 ATE システムとプローバーのこの組み合わせは、単一の基板上に結合され、単一のパッケージ化された IC のように組み立てられるチップレットのテストにも使用されます。シングルチップ プロービングとマルチチップ プロービングのプロセスは同じように見えますが、マルチチップ プロービングの要件は経済的な理由からより厳しくなります。たとえば、90% の最終テスト歩留まりをもたらす単一のダイをプローブすることは十分かもしれませんが、3 チップレット モジュール (各モジュールの歩留まりが 90%) の合計歩留まりは、わずか 73% になります。単一チップでのプローブのエスケープは、良品のパッケージと不良のダイを廃棄することになりますが、モジュール構成では、高価な良品のパッケージと、おそらく 2 つの良好なダイと不良のダイを廃棄することになります。さらに、最終テストの歩留まりが低下するため、テスト全体のコストが増加します。これは、チップレットを包括的に調査することが極めて重要であることを強調しています。

プローブでチップレットとして使用される半導体をテストする際の課題には、次のようなものがあります。

- 既知の良いダイ: 従来、プロービングは故障を選別するために使用され、それによって ATE でのパッケージ テストでの大きな歩留まり低下を回避してきました。 ATE は、完全な検証に適した環境を提供し、プローブ中に検出されなかったものを最終テストで確実にキャッチします。チップレットは、完全なパッケージ内で他のチップレットと組み合わされた後の歩留まりの低下を防ぐために、ダイの形で徹底的に検証される必要があります。これは、プロービング段階でのテストのハードルが、単一ダイパッケージの部品よりもはるかに高いことを意味します。

- シグナルインテグリティ: チップレットは通常の使用時に短距離で信号を駆動するように設計されているため、その I/O は電力効率を考慮して最適化されており、その結果、出力は比較的弱くなります。チップレットをプローブする場合、出力はテスターにラインを駆動する必要があり、これはバッファーの能力を超える要求です。この制限により、テスト時間が大幅に遅くなり、高速でテストできる可能性がなくなります。

- 複雑な相互接続: 多くのチップレットはプロトコル トランスレータとして機能し、最終パッケージ製品が複数のインターフェイスと通信できるようにします。これらの複雑なプロトコルは、ダイレベルで徹底的に検証する必要があります。このため、信号損失のある環境での高速テストが必要になります。

- 複雑なデザイン: チップレットは低ジオメトリの FinFet テクノロジーを頻繁に採用しており、信じられないほど複雑な設計になっています。これらの設計を徹底的にテストすることは、時間がかかり、より困難なプロセスになります。この複雑さは、信号の整合性や相互接続の問題に対応するために I/O の速度を下げる必要があるため、さらに複雑になる可能性があります。

- スループット: チップレットの複雑さと相互接続の課題は、迅速なテストにとって大きな障害となります。理想的には、効率を高めるために複数のダイを並行してプローブすることができます。ただし、チップレットの I/O 数が増加すると、さらに多くのテスター I/O が必要となり、並列テスト プロセスが複雑になります。

プローバーと ATE システムを使用してチップレット テストの課題に対処するには、半導体テストの専門知識、適切な機器の選択、および綿密なテスト手順が必要です。効果的なソリューションには、多くの場合、チップ設計者、テストエンジニア、機器メーカー間の協力が必要です。

チップレットベースの半導体テストに代わる新たな選択肢が登場

Elevate は、チップレットベースの半導体テストにおける新しい戦略を開拓しています。彼らは、特定の半導体を従来の自動テスト装置 (ATE) テスターからプローブ カードに移行することを検討しています。これにより、次のようなテスト上の利点が数多く得られる可能性があります。

- 信号整合性の向上と信号ルーティングの最適化: ピン エレクトロニクスと DPS が DUT に近接しているため、信号経路が短く、損失が少なく、複雑さが軽減され、DUT での信号の完全性が向上します。この高速信号の完全性の向上により、高速テストが可能になり、より包括的なテストと最終テストの歩留まりの向上につながります。さらに、DPS から DUT までの経路が短いため、電源ドループが軽減され、誤ったエラーが排除され、全体的なテストの再現性が向上します。

- テスターの複雑さの軽減: プローブカードの複雑さは増加しますが、テスターの複雑さは減少します。開発者は、テスト対象の特定のチップレットに合わせてプローブ カードを最適化できるため、パフォーマンスが向上し、テスト時間が短縮されると同時に、複雑なテスターが不要になるため資本支出も削減されます。さらに、信号はプローブ カードから発信されるため、複数のテスターおよび構成にわたって「正確なコピー」要件を維持できます。

- テスト時間の短縮: プローブ カードにより多くの PE ピンと DUT ピンを配置すると、より多くの並列テストが可能になり、テスト時間が効果的に短縮されます。

並行テスト: 理想的には、プローブは 1 回のタッチダウンにできるだけ近いところで行われる必要があります。コネクタの制約を排除することで、並列処理を使用できる範囲が大幅に増加し、テスト効率が大幅に向上します。

スケーラビリティ: プローブ カード テスト ソリューションを開発すると、より低い開発コストで同様のチップレットをテストするために活用できます。 - カスタマイズ: プローバーベースのテスト ソリューションは、さまざまなチップレット設計の特定の要件を満たすようにカスタマイズでき、各チップレット構成に合わせた正確なテストを保証します。

- 低い接触抵抗: 接触抵抗はさまざまなプローブ ソリューション間で一貫していますが、追加のセンス ピンを利用できるため、リモート センシングやケルビン センシングが容易になります。この機能は、校正や接触抵抗の補償に役立ちます。

- 柔軟性: プローバーベースのテスト システムは、さまざまなチップレット構成に適応できるため、さまざまなチップレット設計のテストに適しています。

- 互換性: プローブ カードで処理される機能パラメータとパフォーマンス パラメータが増えると、テスターへのインターフェイスの厳格さが緩和されます。これにより、選択したテスター プラットフォームに関係なく、コピーどおりの波形が DUT に存在することが可能になります。

Elevate Semiconductor と協力して、革新的なコラボレーションを通じてチップレット テストの未来を開拓しましょう。

Elevate Semiconductor は、ATE 半導体とプローバー カードを統合することにより、半導体テストの進歩を先駆的に行っています。この技術革新により、シグナル インテグリティの向上、テストの高速化、および多様なチップレット設計に合わせたソリューションの提供が約束されます。当社は、チップレット テストの未来を再構築し、半導体テスト技術の継続的な進化に貢献するために、ATE およびプローバー メーカーとのパートナーシップを積極的に模索しています。