ATE 文章

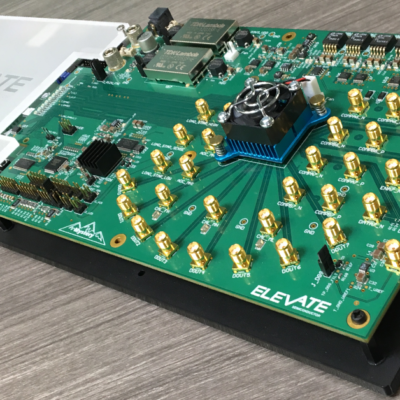

Elevate Semiconductor 提供多样化的产品,评估模块 (EVM) 在评估中发挥着关键作用……

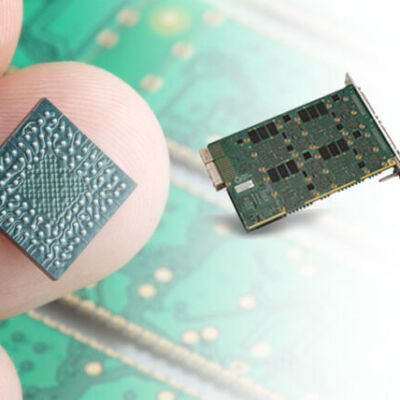

应对半导体小芯片测试中的复杂挑战在半导体技术中,小芯片已经作为模块化组件出现,可以运行……

采访 ElevATE 高速 IC 设计总监 Anthony Turvey 采访者:您是如何进入……的

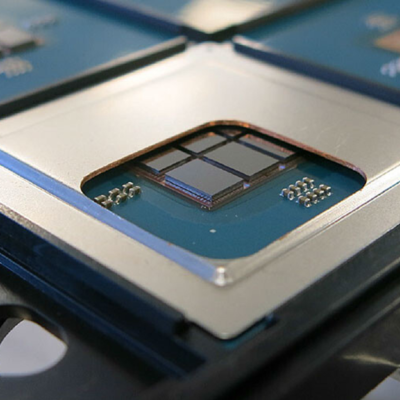

AI 处理器,例如 Graphcore 和 NVIDIA 的 AI Super Chip GH200 等著名型号,展示了强大的计算能力。凭借力量……

作者:Elevate 工程副总裁 Simon Leigh 随着测试变得越来越复杂,ATE 供应商必须不断……

通过测试:芯片背后的芯片。 ENGINEERING.COM 至关重要的 ATE 行业从未面临过如此多的挑战,但像这样的公司......

ATE 数字系统传统上由定序器、格式化器、定时发生器和引脚电子器件组成。关于使用哪些组件的决定......

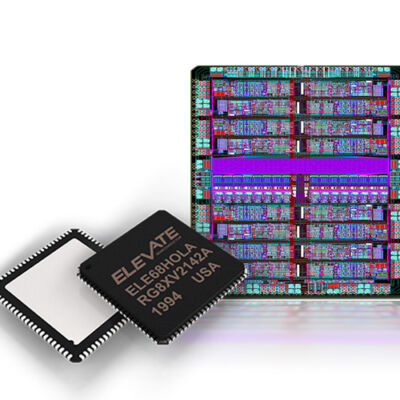

多家半导体公司已在多种不同工艺中提供了用于引脚电子 (PE) 的典型集成电路 (IC) 解决方案……

MIPI 规范和测试 ATE 文章 / 作者:admin 移动行业处理器接口 (MIPI®) 标准定义了设计的行业规范……

随着技术的发展,人工智能、深度学习、机器学习、汽车、物联网、医疗保健等领域对下一代芯片的需求不断增加……

设备电源 (DPS) 半导体提供灵活的电压和电流力测量功能,以满足各种测试...

提升:集成测试技术的世界领先者半导体测试的基础知识:技术爱好者都知道摩尔定律,该定律规定了数字……