ATE 기사

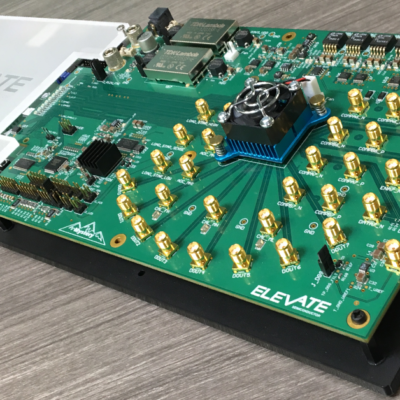

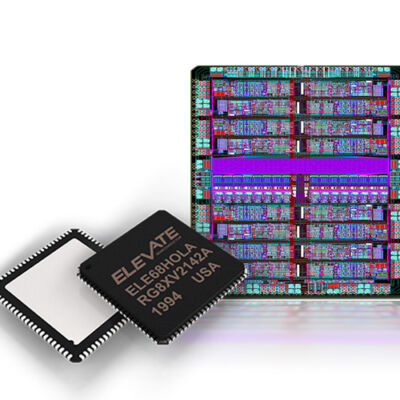

Elevate Semiconductor는 다양한 제품을 제공하며 EVM(평가 모듈)은 평가에서 중추적인 역할을 합니다.

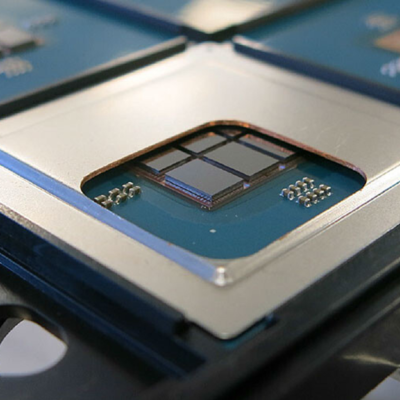

반도체 칩렛 테스트의 복잡한 과제 해결 반도체 기술에서 칩렛은 다음 중 하나로 작동할 수 있는 모듈식 구성 요소로 등장했습니다.

ElevATE의 고속 IC 설계 이사인 Anthony Turvey와의 인터뷰 인터뷰어: 어떻게 이 분야에 참여하게 되셨나요?

Graphcore 및 NVIDIA의 AI Super Chip GH200과 같은 유명 모델과 같은 AI 프로세서는 엄청난 컴퓨팅 성능을 보여줍니다. 힘으로…

Simon Leigh, Elevate 엔지니어링 부사장 테스트가 복잡해짐에 따라 ATE 벤더가 지속적으로…

테스트 통과: 칩 뒤의 칩. ENGINEERING.COM 중요한 ATE 산업은 그 어느 때보다 도전에 직면해 있습니다. 하지만 다음과 같은 기업은…

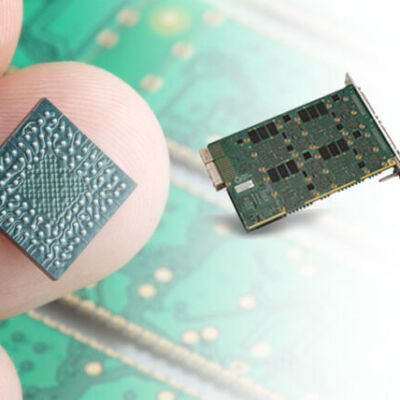

ATE 디지털 시스템은 전통적으로 시퀀서, 포맷터, 타이밍 생성기 및 핀 전자 장치로 구성됩니다. 사용할 구성 요소에 대한 결정…

핀 전자 장치(PE)를 위한 일반적인 집적 회로(IC) 솔루션은 여러 반도체 회사에서 여러 프로세스로 제공되었습니다.

MIPI 사양 및 테스트 ATE 기사 / By admin 모바일 산업 프로세서 인터페이스(MIPI®) 표준은 설계에 대한 산업 사양을 정의합니다.

기술이 발전하고 인공 지능, 딥 러닝, 기계 학습, 자동차, IOT, 의료 분야에서 차세대 칩에 대한 수요가 증가함에 따라…

장치 전원 공급 장치(DPS) 반도체는 유연한 전압 및 전류 힘 측정 기능을 제공하여 광범위한 테스트를 충족합니다.…

ELEVATE: 통합 테스트 기술의 세계적 리더 반도체 테스트의 기초: 기술 애호가들은 수치를 나타내는 무어의 법칙을 알고 있습니다.