ATE digital systems traditionally consist of sequencers, formatters, timing generators and pin electronics. The decision about which components to use for each section of the design is primarily driven by performance specifications and cost desired. These components range from discrete, fully custom ASIC, Field Programmable Gate Array or commercially available parts.

Field Programmable Gate Arrays (FPGA) provide flexibility and have been used for the sequencer and timing/formatting for low to medium performance ATE digital subsystems.

Implementing the sequencer with an FPGA provides flexibility to customize the digital subsystem for logic, memory or mixed signal test. The FPGA clocking required is typically well within the specifications of the target FPGA. The sequencer and pattern execution stages are typically what make each system unique compared to the competitors offering.

The format and timing functionality are typically similar amongst different ATE platforms. The differences are in the cycle to cycle edge placement resolution and accuracy as well as the fine skew control used for channel deskew calibration. The fine deskew control is often available in the pin electronics ICs.

FPGAs have been successfully used for the timing and format function, but the FPGA quickly becomes the limiting factor as the system performance requirements increase to above 50-100Mhz pattern rates and as the system edge placement accuracy is pushed below 1ns. While the SERDES engines in the FPGA I/O structures can provide <100ps resolution, implementing this reliability for edge to edge timing placement increases the design time and pushes the designer to choose larger and more expensive FPGA.

The most common usage of the SERDES blocks are for various communications protocols such as PCIe and the FPGA design tools provide excellent tools for designing and characterizing these functions. Designers often run into roadblocks when designing the timing section using these SERDES blocks and there are limited tools available from FPGA vendors to resolve issues. Designers often spend 10X the budgeted engineering hours implementing and characterizing these timing circuits. Typical issues include: inconsistent linearity from channel to channel, higher than acceptable jitter, and difficulty routing the design from run to run.

As designers attempt to increase the channel count they are required to migrate to larger and more expensive FPGAs. In the past, designers have been able to capitalize on faster and larger FPGAs at lower costs. In recent times, however, the focus of FPGA companies has been to increase compute capabilities to address the data center and artificial intelligence markets. This addition of more compute elements has increased the costs with minimal or negative benefits to the ATE designer. In addition, the costs of older devices that serve the ATE market have started going up dramatically especially for larger devices. This has pushed the cost for higher channel ATE using larger FPGAs up to $50/channel just for the FPGA.

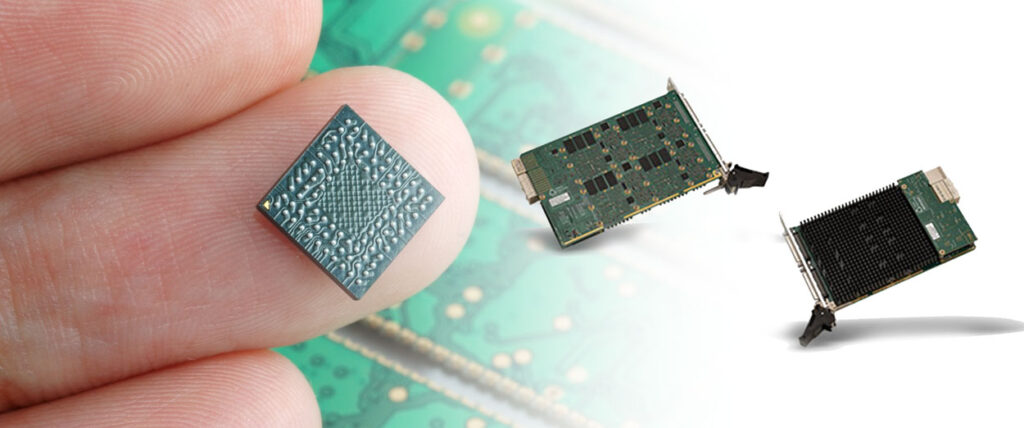

To achieve higher performance ATE with pattern rates of 200+ MHz, ATE designers need to use custom or commercially available format and timing generator ICs. They are then able to use a reasonable cost FPGA for the sequencer portion of the design.

A commercially available timing generator would provide smaller ATE companies to migrate up the performance ladder in digital ATE instrumentation. These chips are designed to be interfaced to high performance pin drivers without requiring an over constrained FPGA I/O.

By purchasing timing chips with high end performance this would reduce the design, characterization and test times as well as reducing the cost per channel while offering higher performance digital ATE specifications. The timing accuracy is specified by the vendor and does not require extensive characterization and production testing of these parameters at system test.

Commercial timing chips will ultimately save an ATE company development cost and time to market as well as overall cost of the system, while providing a path to higher end performance.