ATE 数字系统传统上由定序器、格式化器、时序发生器和 针电子。关于设计的每个部分使用哪些组件的决定主要取决于性能规格和所需的成本。这些组件包括分立的、完全定制的 ASIC、现场可编程门阵列或市售部件。

现场可编程门阵列 (FPGA) 提供灵活性,已用于中低性能 ATE 数字子系统的定序器和定时/格式化。

使用 FPGA 实现定序器可以灵活地定制用于逻辑、存储器或混合信号测试的数字子系统。所需的 FPGA 时钟通常完全符合目标 FPGA 的规格。与竞争对手的产品相比,定序器和模式执行阶段通常是每个系统的独特之处。

不同 ATE 平台的格式和计时功能通常相似。差异在于周期间边缘放置分辨率和精度以及用于通道相差校正校准的精细相差控制。引脚电子 IC 中通常提供精细的相差校正控制。

FPGA 已成功用于定时和格式功能,但随着系统性能要求提高到 50-100Mhz 模式速率以上以及系统边缘布局精度降至 1ns 以下,FPGA 很快成为限制因素。虽然 FPGA I/O 结构中的 SERDES 引擎可以提供 <100ps 的分辨率,但实现这种边缘到边缘时序布局的可靠性会增加设计时间,并促使设计人员选择更大、更昂贵的 FPGA。

SERDES 模块最常见的用途是用于各种通信协议,例如 PCIe,FPGA 设计工具为设计和表征这些功能提供了出色的工具。设计人员在使用这些 SERDES 模块设计时序部分时经常会遇到障碍,并且 FPGA 供应商提供的用于解决问题的工具有限。设计人员通常花费 10 倍的预算工程时间来实现和表征这些定时电路。典型问题包括:通道与通道之间的线性度不一致、高于可接受的抖动以及运行与运行之间的设计布线困难。

当设计人员尝试增加通道数时,他们需要迁移到更大、更昂贵的 FPGA。过去,设计人员能够以更低的成本利用更快、更大的 FPGA。然而,近年来,FPGA 公司的重点是提高计算能力,以满足数据中心和人工智能市场的需求。添加更多计算元件增加了成本,但对 ATE 设计人员来说却几乎没有好处或带来负面好处。此外,服务于 ATE 市场的旧设备的成本已开始急剧上升,尤其是大型设备。这使得使用更大 FPGA 的更高通道 ATE 的成本高达 $50/通道(仅针对 FPGA)。

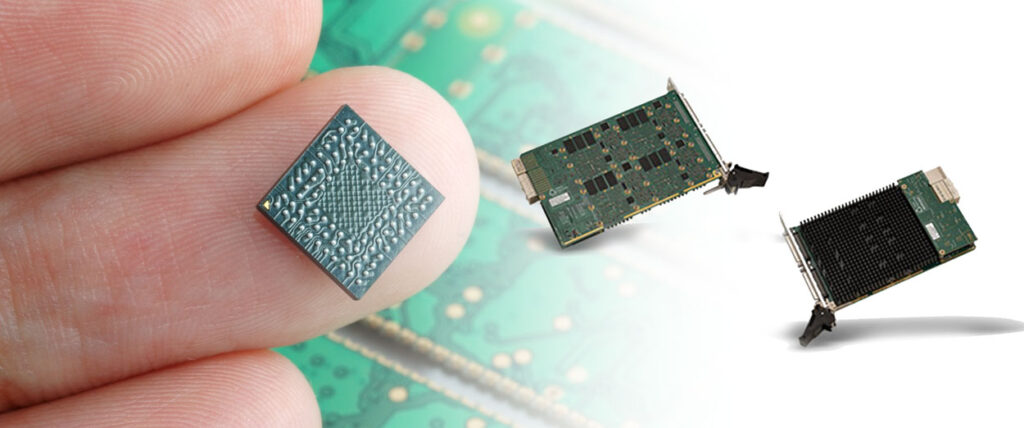

为了实现模式速率超过 200 MHz 的更高性能 ATE,ATE 设计人员需要使用定制或商用格式和时序发生器 IC。然后,他们能够将成本合理的 FPGA 用于设计的定序器部分。

商用定时发生器将帮助规模较小的 ATE 公司升级数字 ATE 仪器的性能阶梯。这些芯片设计用于连接高性能引脚驱动器,而不需要过度约束的 FPGA I/O。

通过购买具有高端性能的计时芯片,可以减少设计、表征和测试时间,并降低每个通道的成本,同时提供更高性能的数字 ATE 规格。时序精度由供应商指定,不需要在系统测试时对这些参数进行广泛的表征和生产测试。

商业计时芯片最终将节省 ATE公司 开发成本和上市时间以及系统的总体成本,同时提供实现更高最终性能的途径。