行政

ElevATE Semiconductor 欢迎 Heather Kirkby 加入董事会,增强领导力和战略愿景 ElevATE Semiconductor 是一家领先的设计和……

新闻稿 ElevATE Semiconductor 和 GlobalFoundries 合作开发用于商业和国家安全应用的高压芯片根据客户需求,…

我们很高兴地宣布我们将参加 6 月 3 日至 5 日在加利福尼亚州卡尔斯巴德举行的 SWTEST 2024。这是……

我们很荣幸地宣布任命 Jan Gaudestad 为 Elevate Semiconductor 新任首席执行官,该任命立即生效。Jan…

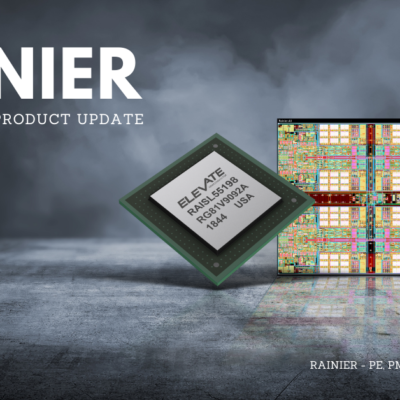

作者:Anthony Turvey – 高速 IC 设计总监 ElevATE 自豪地宣布,1.6Gbps 的开发……

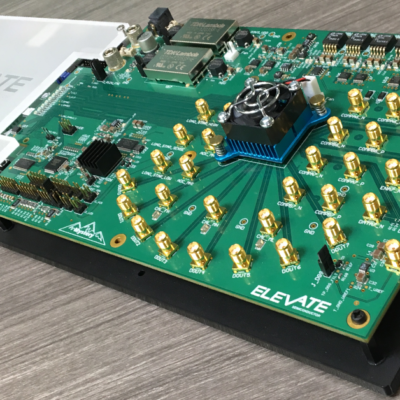

Elevate Semiconductor 提供多样化的产品,评估模块 (EVM) 在评估中发挥着关键作用……

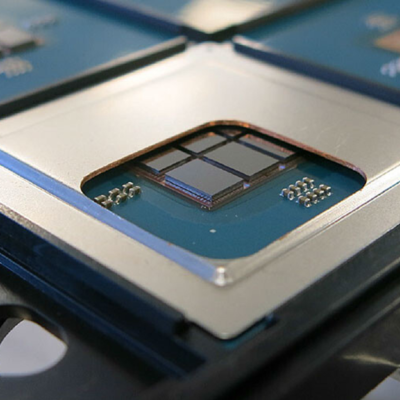

应对半导体小芯片测试中的复杂挑战在半导体技术中,小芯片已经作为模块化组件出现,可以运行……

采访 ElevATE 高速 IC 设计总监 Anthony Turvey 采访者:您是如何进入……的

AI 处理器,例如 Graphcore 和 NVIDIA 的 AI Super Chip GH200 等著名型号,展示了强大的计算能力。凭借力量……

作者:Elevate 工程副总裁 Simon Leigh 随着测试变得越来越复杂,ATE 供应商必须不断……

ElevATE Semiconductor 庆祝由 Presidio Investors 和 Kline Hill Partners 牵头的持续基金成功募集,德克萨斯州奥斯汀,5 月 9 日……