SEMICONDUCTORS | AI | DESIGN | PACKAGING | MEMS | DISPLAYS

SEMICONDUCTOR DIGEST

### NEWS AND INDUSTRY TRENDS

JULY 2023

Testing Semiconductors with 5nm and Smaller Geometries p. 20

Carbon Capture, Utilization, and Storage Technology p. 28

Measuring the Critical W-recess in 3D NAND p. 31

Evaluating STT-MRAM Chips for Automotive Applications p. 43

# **The State of the State of the**

### Big Ideas, The Best Team, The Right Solutions.

### Nikon. Technology to Do More.

The world has changed dramatically, and Nikon recognizes that technology must do more to serve society and our planet.

Our semiconductor lithography and inspection systems bring together the winning combination of over a century of Nikon innovation and the most dedicated employees in the world to deliver the right solutions for our customers.

<image>

www.nikonprecision.com

Visit us at SEMICON West 2023 July 11-13, 2023 - Booth #1028 South Hall

# SEMICONDUCTOR DIGEST

### NEWS AND INDUSTRY TRENDS

July 2023 Volume 5 Number 5

**COVER:** ElevATE Semiconductor is pioneering next-generation solutions for semiconductor testing. Shown (left to right): David Kenyon: CEO, Simon Leigh: VP of Engineering, and Tim Bakken: VP of Global Sales.

### Columns

### **4 EDITORIAL**

AI in Semiconductor Manufacturing PETE SINGER, EDITOR-IN-CHIEF

#### 56 INDUSTRY OBSERVATION Indium Plating Challenges: Unlocked JOHN GHEKIERE, VICE PRESIDENT, PRODUCT & TECHNOLOGY, CLASSONE TECHNOLOGY

### Departments

6 NEWS

54 AD INDEX

### **FEATURES**

### **20 TEST**

### **Challenges in Testing Semiconductors** with 5nm and Smaller Process Geometries

Elevate Semiconductor's latest DPS/PMU products offer improved architectures to maximize power efficiency, while providing high channel counts and DC accuracy necessary to test tomorrow's state-of-the-art devices.

### 22 TRENDS

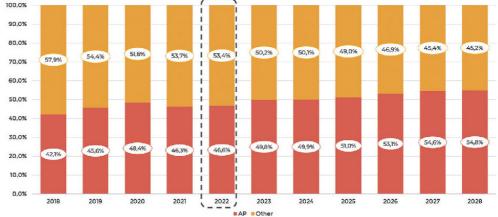

### The State of the Semiconductor Industry 2023

New approaches will be required to address challenges associated with energy efficiency, the explosion of AI and emerging automotive applications. PETE SINGER, EDITOR-IN-CHIEF

### **28 SUSTAINABILITY**

### Carbon Capture, Utilization, and Storage Technologies' Role in Fighting Global Warming

Carbon capture, utilization, and storage (or sequestration) (CCUS) refers to various technologies that capture carbon dioxide at a source or from the atmosphere (direct air capture) and then either use it or store it so that it does not contribute to warming the planet. CHRIS JONES, EDWARDS VACUUM

### **31 METROLOGY**

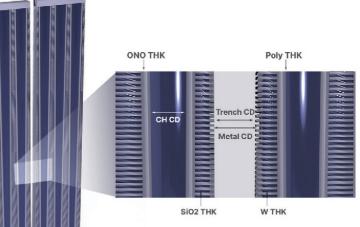

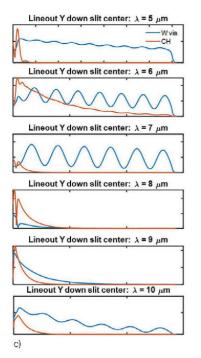

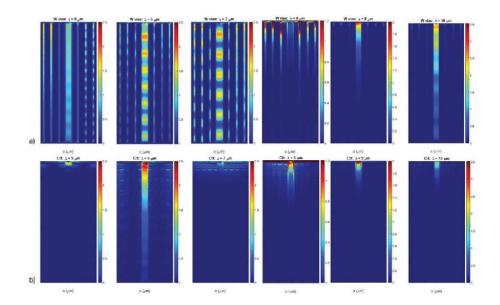

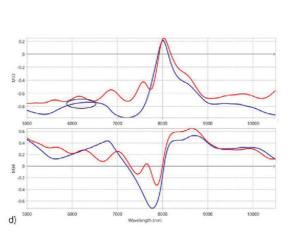

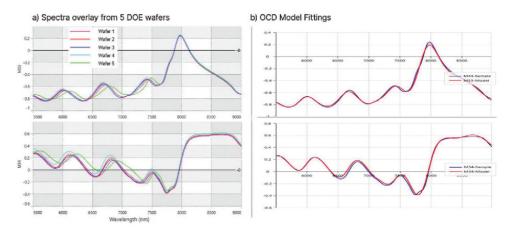

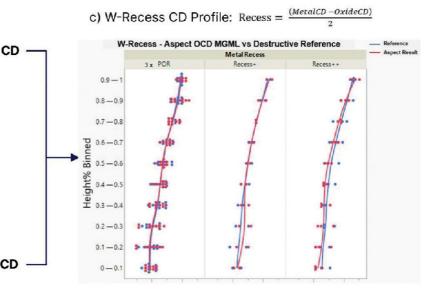

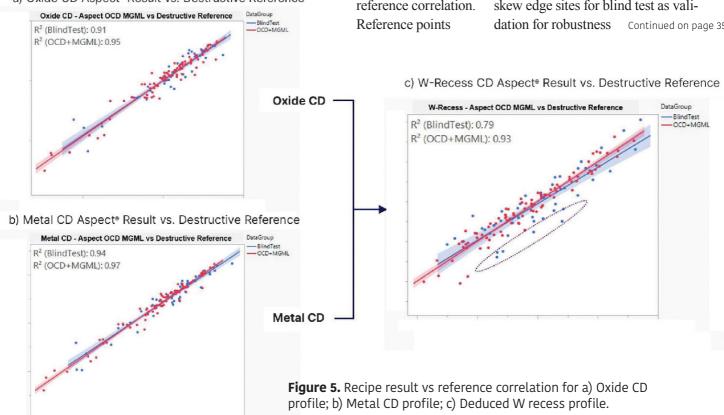

### Measuring the Critical W-recess in 3D NAND

A new technique that uses a specialized via to periphery target structure overcomes limitations of existing approaches. NICK KELLER, ZHUO CHEN, PETER WANG, ROSTISLAV GRYNKO, TROY RIBAUDO, G. ANDREW ANTONELLI AND YOUCHENG WANG, ONTO INNOVATION, INC.

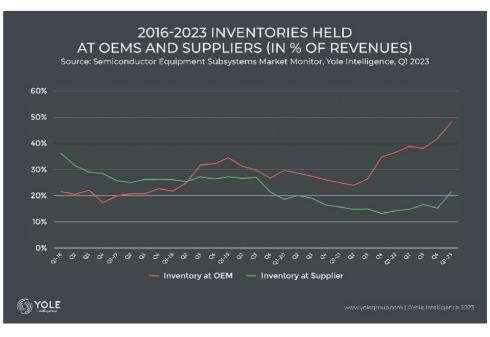

#### **36 SUPPLY CHAIN**

### Semi-cap Supply Chain Overshoots

Suppliers take advantage of the slowdown to get back on track. JOHN WEST, SENIOR DIRECTOR OF THE SEMICONDUCTOR SUBSYSTEMS AND TEST DIVISION, YOLE GROUP.

#### **37 TEST**

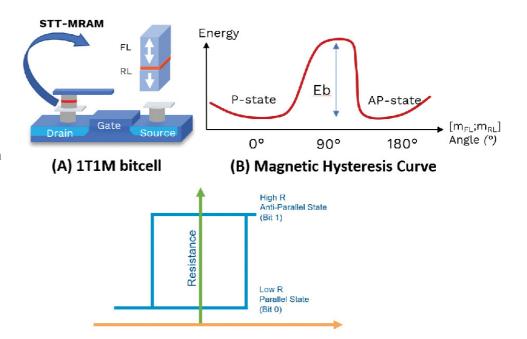

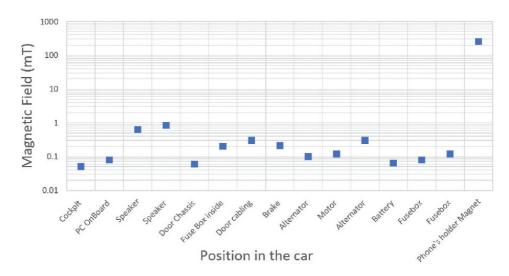

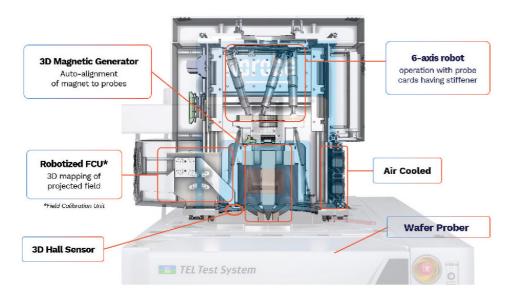

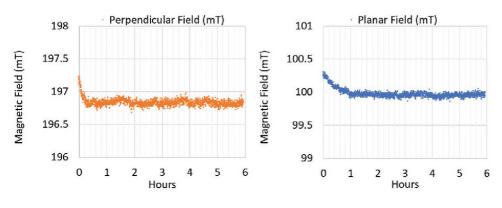

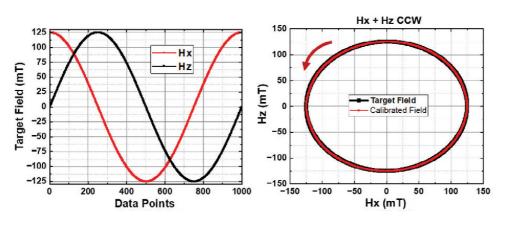

### Magnetic Resilience in Motion: Evaluating STT-MRAM Chips for Automotive Applications

A replacement memory technology — magnetic random-access memory (MRAM) — has been introduced and is today under adoption by car chipmakers as it answers system requirements for more advanced vehicles. SIAMAK SALIMY, CO-FOUNDER AND CTO OF HPROBE

#### **40 MEMORY**

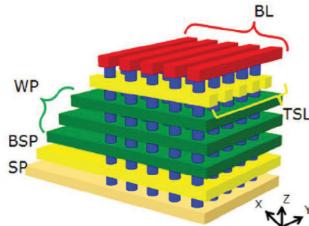

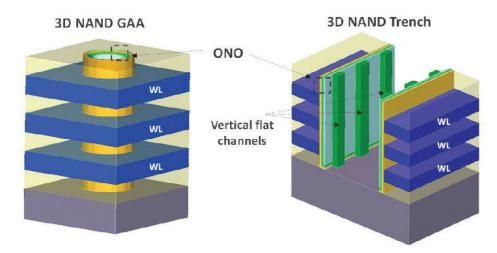

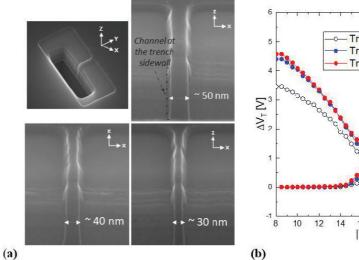

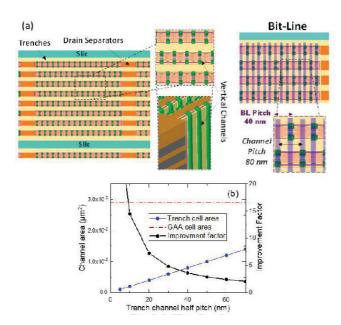

### Imec Improves Memory Window of a 3D Trench Cell for Next-gen NAND Flash

The results mark a milestone in enabling ultrahigh-density trench-based 3D NAND Flash memories. MAARTEN ROSMEULEN, PROGRAM DIRECTOR OF THE STORAGE MEMORY PROGRAM, IMEC

**40**

#### **43 AUTOMOTIVE**

### Semiconductors for Automobiles: New Challenges Ahead

Distributed architectures, AI, wideband gap materials, chiplets and higher frequency devices are just some of the new technologies driving a new era of innovation and collaboration between car makers and chip makers. **PETE SINGER**, **EDITOR-IN-CHIEF**

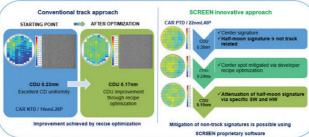

### **47 LITHOGRAPHY**

### **SCREEN Brings Patterning Solutions for Advanced Lithography**

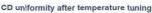

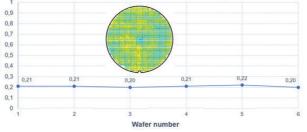

New software improve targeted spatial locations on the wafer to provide more uniform features across the surface. HAROLD STOKES, SENIOR MARKETING MANAGER, SCREEN

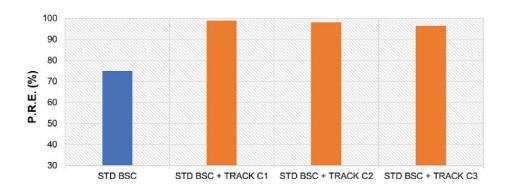

#### **50 PACKAGING**

### Advanced Packaging: Fueling the Next Era of Semiconductor Innovation

Advanced packaging technologies are well-positioned to address the evolving demands of high-performance computing, AI and 5G. BILAL HACHEMI, TECHNOLOGY & MARKET ANALYST,

ADVANCED PACKAGING AT YOLE INTELLIGENCE.

We continuously strive to minimise the environmental impact of the semiconductor industry in our natural world and environment we live in now and for our future.

### Editorial

### **AI in Semiconductor Manufacturing**

RTIFICIAL INTELLIGENCE IS POISED TO IMPACT VIRTUALLY every aspect of our lives moving forward. It's also playing an increasingly important role in the manufacturing of semiconductors.

At the recent imec-hosted ITF World held in Antwerp, Belgium in May, Jensen Huang, president, CEO and Member of the Board of Directors at NVIDIA, gave some insights into how NVIDIA is working with companies such as TSMC, ASML, Applied Materials (AMAT), D2S, IMS Nano Fabrication and Synopsys to bring AI to chip making.

"The first wave of AI that focused on computer vision and speech recognition has achieved superhuman capabilities and has opened up multi-trillion dollar opportunities in robotics, autonomous vehicles and manufacturing," Huang said. "Advanced chip manufacturing requires over a thousand steps, producing features the size of a biomolecule. To make chips with quadrillions of features, each step must be nearly perfect to yield any output. Sophisticated computational sciences are performed at every stage to compute the features to be patterned and to do defect detection for inline process control. Chip manufacturing is an ideal application for NVIDIA accelerated computing and AI."

Huang said D2S and IMS Nano Fabrication build mask writers using e-beams to create photoresist patterns on a mask. "Nvidia GPUs do the pattern rendering and mask process correction," he said. TSMC and KLA use EUV and DUV illumination for mask inspection. "NVIDIA GPUs process classical physics modeling, and deep learning to generate synthetic reference images and detect defects," he said.

KLA and AMAT use NVIDIA for their e-beam wafer inspection systems and for their optical wafer inspection systems, which detect defects smaller than the pixel. "The data rate is extremely high at 40 gigapixels per second to achieve this as part of process control," Huang said.

TSMC, ASML, Synopsys and NVIDIA recently announced plans to accelerate computational lithography. "Computational lithography simulates Maxell's equations of light passing through optics and interacting with photoresists. It is a vital step in chip making and the largest computational workload in chip design and manufacturing, consuming tens of billions of CPU hours annually," Huang said, noting that massive data centers run 24/7 to create reticles for new chips. "We have already accelerated the processing by 50 times," he added.

Christophe Fouquet, CBO & Board of Management at ASML, who also spoke at ITF World said that, in the last few years, the company has shifted to AI and massive use of metrology. What does it mean? The number of parameters we use in our models to describe the litho process have increased by a factor of 800," he said. He said in ASML's scanners, more than 50,000 parameters can be tuned for every die exposed. "It's allowed us to improve our accuracy, alignment and overlay," he said.

AI is being used to make AI chips — the cobbler's children have some fine new shoes, indeed!

-Pete Singer, Editor-in-Chief

#### SEMICONDUCTOR DIGEST

NEWS AND INDUSTRY TRENDS

Kerry Hoffman, Publisher kerryh@semiconductordigest.com 978-580-4205

Pete Singer, Editor-in-Chief psinger@semiconductordigest.com 978-470-1806

**Shannon Davis, Web and News Editor** sdavis@semiconductordigest.com

For subscription information, please visit www.semiconductordigest.com/subscribe.

Dave Lammers, Contributing Editor dplammers@att.net

John Blyler, Contributing Editor jblyler@semiconductordigest.com

Dick James, Contributing Editor dickjames@siliconics.ca

**Cindy Chamberlin, Art Director**

#### Rich Mehta, Website Design

July 2023 VOL. 5 NO. 5 • Semiconductor Digest ©2023 ISSN 2643-7058 (print) ISSN 2643-7074 (online). Semiconductor Digest is published eight times a year by Gold Flag Media LLC, 58 Summer St., Andover, MA 01810. Copyright © 2023 by Gold Flag Media LLC. All rights reserved. Printed in the U.S.

www.semiconductordigest.com

### **Speed is your friend.** Dramatically speed up semiconductor tool alignment.

# Improve yields and tool up time while saving time and expense.

Introducing the next-generation, wireless WaferSense® and ReticleSense® Auto Teaching System™ (ATS2™/ATSR™) with CyberSpectrum™ software.

Signicantly faster multi camera system teaching for accurate wafer and reticle hand-off calibration, proper alignment, and set-up for semiconductor tools. ATS2 and ATSR "see" inside in real-time to capture three dimensional off-set data (x, y and z) to quickly teach wafer and reticle transfer positions - all without opening the tools.

www.cyberoptics.com Copyright © Nordson Corporation. All rights reserved.

# news

### Global 300mm Fab Equipment Spending Forecast to Reach Record \$119 Billion in 2026, SEMI Reports

Global 300mm fab equipment spending for front-end facilities next year is expected to begin a growth streak to a US\$119 billion record high in 2026 following a decline in 2023, SEMI highlighted in its quarterly 300mm Fab Outlook Report to 2026. Strong demand for high-performance computing, automotive applications and improved demand for memory will fuel double-digit spending in equipment investments over the three-year period.

After the projected 18% drop to US\$74 billion this year, global 300mm fab

equipment spending is forecast to rise 12% to \$US82 billion in 2024, 24% to US\$101.9 billion in 2025 and 17% to US\$118.8 billion in 2026.

"The projected equipment spending growth wave underscores the strong secular demand for semiconductors," said Ajit Manocha, SEMI President and CEO. "The

foundry and memory sectors will figure prominently in this expansion, pointing to demand for chips across a wide breadth of end markets and applications."

#### **Regional growth**

Korea is expected to lead global 300mm fab equipment spending in 2026 with US\$30.2 billion in investments, nearly doubling from US\$15.7 billion in 2023. Taiwan is forecast to invest US\$23.8 billion in 2026, up from US\$22.4 billion this year, and China is projected to log US\$16.1 billion in spending in 2026, an increase from US\$14.9 billion in 2023. Americas equipment spending is expected to nearly double from US\$9.6 billion this year to US\$18.8 billion in 2026.

#### Segment growth

Foundry is projected to lead other segments in equipment spending at US\$62.1 billion in 2026, an increase from US\$44.6 billion in 2023, followed by memory at US\$42.9 billion, a 170% increase from 2023. Analog spending is forecast to increase from US\$5 billion this year to US\$6.2 billion in 2026. The microprocessor/microcontroller, discrete (mainly power devices), and optoelectronics segments are expected to see spending declines in 2026, while investments in logic are forecast to rise.

The SEMI 300mm Fab Outlook Report To 2026 report lists 369 facilities and lines globally, including 53 high-probability facilities expected to start operation during the four years starting in 2023. So

### SK hynix Begins Mass Production of 238-Layer 4D NAND

SK hynix Inc. has started mass production of its 238-layer 4D NAND Flash memory, following the development in August 2022, and that product compatibility test with a global smartphone manufacturer is underway.

"SK hynix has developed solution products for smartphones and client SSDs which are used as PC storage devices, adopting the 238-layer

NAND technology, and has moved into mass production in May," the company said. "Given that the company secured world-class competitiveness in price, performance and quality for both 238-layer NAND and the previous generation 176-layer NAND, we expect these products to drive earnings improvement in the second half of the year."

The 238-layer product — the smallest NAND in size — has a 34% higher manufacturing efficiency compared to the previous generation of 176-layer, resulting in a significant improvement in cost competitiveness.

Besides, with a data-transfer speed Continued on page 10

### YOUR COMPLETE SUBFAB PARTNER.

Vacuum pumps. Gas abatement. Leak detection. Global service.

VISIT US AT SEMICON WEST BOOTH# 541

**From load lock pump down to the harshest byproduct processes**, Busch provides leading semiconductor Fabs with vacuum pumps and abatement solutions, full SubFab management, and support tailored to your needs.

Ŀ1.

Contact us today! Scan to learn more

1-800-USA-PUMP | info@buschusa.com | **buschusa.com**

### **Global Semiconductor Materials Market Revenue Reaches Record \$73 Billion in 2022**

Global semiconductor materials market revenue grew 8.9% to \$72.7 billion in 2022, surpassing the previous market high of \$66.8 billion set in 2021, SEMI, the global industry association representing the electronics manufacturing and design supply chain, reported in its Materials Market Data Subscription (MMDS).

Wafer fabrication materials and packaging materials revenue in 2022 reached \$44.7 billion and \$28.0 billion, respectively, increasing 10.5% and 6.3%. The silicon, electronic gases, and photomask segments showed the strongest growth in the wafer fabrication materials market, while the organic substrates segment largely drove packaging materials market growth.

For the 13th consecutive year, Taiwan, at \$20.1 billion, was the world's largest consumer of semiconductor materials on the strength of its foundry capacity and advanced packaging base. China continued to register strong yearover-year results, ranking second in 2022, while Korea finished as the third largest consumer of semiconductor materials. Most regions registered high single- or double-digit growth last year.

The Materials Market Data Subscription (MMDS) from SEMI provides annual revenue with 10 years of historical data and a two-year forecast. The annual subscription includes quarterly updates for the materials segment and reports revenue for seven market regions (North America,

|               | 2021**   | 2022     | YEAR-<br>OVER-YEAR |

|---------------|----------|----------|--------------------|

| TAIWAN        | \$17,715 | \$20,129 | 13.6%              |

| CHINA         | \$12,082 | \$12,970 | 7.3%               |

| SOUTH KOREA   | \$12,134 | \$12,901 | 6.33%              |

| REST OF WORLD | \$7,896  | \$8,627  | 9.3%               |

| JAPAN         | \$7,275  | \$7,205  | -1.0%              |

| NORTH AMERICA | \$5,713  | \$6,278  | 9.9%               |

| EUROPE        | \$3,961  | \$4,580  | 15.6%              |

| TOTAL         | \$66.776 | \$72,691 | 8.9%               |

Source: SEMI (www.semi.org), Juen 2023

Note: Summed subtotals may not equal the total due to rounding. \*Rest of World inculdes Singapore, Malaysia, Philippines, other areas of Southeast Asia and smaller global markets. \*\*2021 data reflects current updates.

Europe, Japan, Taiwan, South Korea, China and Rest of World). The report also features detailed historical data for silicon shipments and revenues for photoresist, photoresist ancillaries, process gases and lead frames. So

### Micron, STEMM Opportunity Alliance and NSF Advance New Workforce Development Collaborations

Micron Technology, Inc., one of the world's largest semiconductor companies and the only U.S.-based manufacturer of memory, announced the Northwest University Semiconductor Network, a partnership focused on collectively developing the next generation of the U.S. semiconductor industry's workforce. The network will drive foundational and emerging research to increase students' opportunities for experiential learning across the semiconductor ecosystem, with equitable access for underrepresented students, including those in rural and tribal communities.

On June 12<sup>th</sup>, the STEMM Opportunity Alliance (SOA) held its Northwest STEMM Summit: Achieving Equity and Excellence, hosted by Micron, in Boise. At this summit, Erwin Gianchandani, National Science Foundation's assistant director for technology, innovation and partnerships, and Travis York, SOA leader and director of inclusive STEMM ecosystems for equity and diversity at the American Association for the Advancement of Science (AAAS), joined Micron executives as they introduced the network, which includes 13 founding member institutions across six states.

The SOA is a national initiative led by the AAAS, with support from the Doris Duke Foundation, more than a dozen funders and 110+ cross-sector partners that are focused on galvanizing stakeholders to build a STEMM (science, technology, engineering, mathematics and medicine) ecosystem rooted in equity, inclusion and scientific excellence. The SOA was launched at a White House summit in December 2022 alongside advisory council members, including April Arnzen, Micron senior vice president, chief people officer and president of the Micron Foundation. The SOA and Micron understand that diversity in STEMM is essential to excellence in the scientific ecosystem, which is critical for U.S. economic growth and competitiveness and necessary for building a better society that benefits all communities.

Micron and National Science Foundation (NSF) also announced the next step in a previously disclosed \$10 million partnership between the Micron Foundation and NSF. NSF will publish a Dear Colleague Letter with two NSF solicitations that are focused on educator equity and are aligned with the strategic vision laid out in the CHIPS and Science Act. The first of these solicitations, Research Experiences for Teachers (RET), looks to facilitate professional development of K-12 science teachers through research experience. And the second, the Robert Noyce Teacher Scholarship Program (Noyce), addresses the critical need for recruiting, preparing and retaining highly effective elementary

and secondary mathematics and science teachers in high-need school districts.

"Partnerships between institutions of higher education, government and industry leaders like Micron are critical so that together, we can build an inclusive and robust talent pipeline equipped with the high-tech skills that will advance U.S. technology innovation and leadership," Arnzen said. "Micron is proud to be expanding our university partnership model through the U.S., leveraging the regional proximity to our leading research and development center in Boise and reaching students that have been traditionally underrepresented in the semiconductor industry, including rural and tribal communities in the Northwest. Our partnership with NSF aims to increase diversity and equity among STEM professionals, helping more students from traditionally underrepresented groups see themselves in their educators, the STEM field

and the semiconductor industry. We look forward to furthering the impact of Micron's Northwest University Semiconductor Network and our NSF partnerships as we focus on building a workforce of the future."

Micron plans to invest approximately \$15 billion through the end of the decade to construct a leading-edge memory manufacturing fab co-located with the company's R&D epicenter in Boise. This project will create over 17,000 new Idaho jobs, furthering the need for a diverse, highly-skilled workforce. To support the semiconductor industry at scale, Micron has prioritized building relationships with K-12 and higher education partners who can help train students in STEM disciplines, expand research in the broad field of semiconductors and retain a more diverse group of students as they complete their degrees.

"Public-private partnerships help the

### ELECTRONIC FLUOROCARBONS

- > High Purity Specialty Gases and Advanced Materials

- Rare Gas Center of Excellence

- Low GWP Replacements

- Broad Product Portfolio with Strategic Inventories

- Secure Supply Chain and Global Sourcing Strategy

- State-of-the-Art R&D Lab

- ISO 9001:2015 Accredited

Solution Provider

Independent US Domestic Supplier

Best in Class Data

Sustainability and Innovation

#### Continued from page 6

of 2.4Gb per second, a 50% increase from the previous generation, and approximately 20% increase in read and write speed, the company is confident that it will be able to deliver an improved performance to the smartphone and PC customers using this technology.

Once the product compatibility test with the global smartphone manufacturer is completed, SK hynix will begin supplying the 238-layer NAND product for smartphones,

U.S. stay competitive in key technology areas and grow access to high-wage, good-quality jobs in every part of the country," Gianchandani said. "NSF is delighted to partner with Micron to catalyze new career pathways, including through practical experiences for learners of all backgrounds, ages and geographic locations. The new funding opportunity that we are releasing today will broaden participation in the semiconductor workforce and help create opportunities everywhere and unleash innovation anywhere."

"Both the Northwest University Semiconductor Network and the partnership between Micron and the NSF embody the kind of cross-sector and public-private collaboration necessary to achieving equity and excellence in STEMM," York said. "Investing in the critical semiconductor industry and ensuring we have a diverse workforce that can meet the moment is paramount. SOA looks forward to continued work with our diverse group of partners to build a STEMM ecosystem that will maintain American competitiveness and better individual lives."

The founding partners of the Northwest University Semiconductor Network were identified based on their strong collective undergraduate and graduate programs in engineering and other STEM degrees, as well as on their vast R&D expertise and hands-on learning opportunities for students. The network collectively offers access to teaching labs and cleanrooms, a strong foundation of collaboration across institutions, programs connecting to community colleges and strong diversity programs to increase equitable access to engineering education.

The Northwest University Semiconductor Network will expand and prepare the next generation of talent through a framework centered on collaboration, innovation and problem-solving. Micron, in partnership with the network institutions and in alignment with the American Semiconductor Academy and the SEMI Foundation, will champion

and expand the technology across its product portfolio such as PCIe 5.0\* SSDs and high-capacity server SSDs going forward.

"We will continue to overcome NAND technology limitations and increase our competitiveness so that we can achieve a bigger turnaround than anyone else during the upcoming market rebound," said Jumsoo Kim, Head of S238 NAND at SK hynix.50

> efforts to modernize and enhance curriculum by sharing best practices and industry-backed technical content, expanding experiential learning programs for greater access to cleanrooms and teaching labs, and bolstering research opportunities for students.

A full list of founding partners of the Northwest University Semiconductor Network follows:

- Boise State University

- Idaho State University

- Montana State University

- Oregon State University

- Portland State University

- San José State University

- University of California, Berkeley

- University of California, Davis

- University of Idaho

- University of Oregon

- University of Utah

- University of Washington

- Washington State University In April 2023, Micron announced its Northeast counterpart network to support company plans to invest up to \$100 billion in a megafab in New York. \$100

NEHO: Developing an Artificial Neuron Based on Semiconductor Technology

A tailored combination of material science and photonics to build low energy-consuming neuronal networks is the main goal of the EU-funded project NEHO, coordinated by IIT-Istituto Italiano di Tecnologia (Italian Institute of Technology) in Lecce. The project has been financed with 3 million euros for the next 3 years.

NEHO (Neuromorphic computing Enabled by Heavily doped semiconductor Optics) will exploit semiconductors' properties to create an artificial neuron that can be used to build ultrafast optical neural networks, thus providing a novel and less energy-consuming computational source.

The project will contribute to the

transition from electron-based information processing to an all-photonbased solution: in fact, a photon-based system would, in principle, be much faster, and require a fraction of the energy used by current technologies.

When photons interact with the matter, they generate considerably less heat, but due to their nature, the interaction is weak, such that it is very hard to control the photon flow at small scales. Therefore, NEHO researchers will take advantage from hybrid electron-photon quasi-particles, called *plasmons*, which arises from the interaction of electrons with the light. Plasmons will be produced by using heavily doped semiconductors shone

with mid infrared light. Because a plasmon carries both an electron and a photon, one can act on the electronic part, which is generally easier to do, to induce a change on the photonic counterpart. This kind of interaction permits in principle to control the photons at small scales.

The project revolves around the idea of exploiting effects that occur at the surface, rather than the bulk of the semiconductors, as these can be easily modulated by controlling the electron density on the semiconductor surface. Like waves caused by the wind on the surface of the ocean do not require to move water in the deep. This feature will be used to exploit the implementation of a neural network into the development of new machine learning optimization techniques.

NEHO's ultimate goal is to improve the computational power of innovative technologies, such as those based on artificial intelligence algorithms, and at the same time reduce their energy footprint.

"We could revolutionize the way we process information by developing an innovative photonic integrated circuit platform" — explains Dr. Cristian Ciraci, leader of the Computational Nanoplasmonics unit at IIT in Lecce and NEHO's coordinator. "This platform leverages nonlinear photon-plasmon semiconductor technology to allow ultrafast and energy-efficient information processing in the mid-infrared range. With this project, we could be entering a new era of information processing that is faster, more energy-efficient, and more flexible than ever before".

The NEHO European consortium includes Istituto Italiano di Tecnologia (Italy, coordinator), Ludwig-Maximilians-Universität München (Germany), Universiteit Gent (Belgium), CNRS and Université Paris-Saclay (France), Consiglio Nazionale delle Ricerche (Italy). S

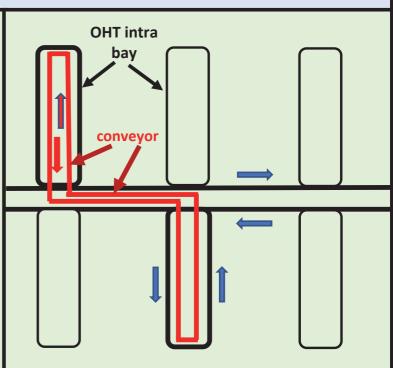

### **CONVEYORS FIX AMHS BOTTLENECKS**

★ FOR BETTER PROCESS COUPLING

★ REDUCED CYCLE TIME

★ INCREASED THROUGHPUT

★ SAVED STOCKER AND EFEM COSTS

The Midsx digiflow conveyors seamlessly fit into your existing AMHS Complementing your OHT-s and your MCS with its embedded controls

Call for free solution consulting and cost estimating.

65 YEARS OF MIDDLESEX INDUSTRIES, WRITE or Call: info@midsx.com or 978-992-2189

### Entegris Breaks Ground for Manufacturing Center in Colorado Springs

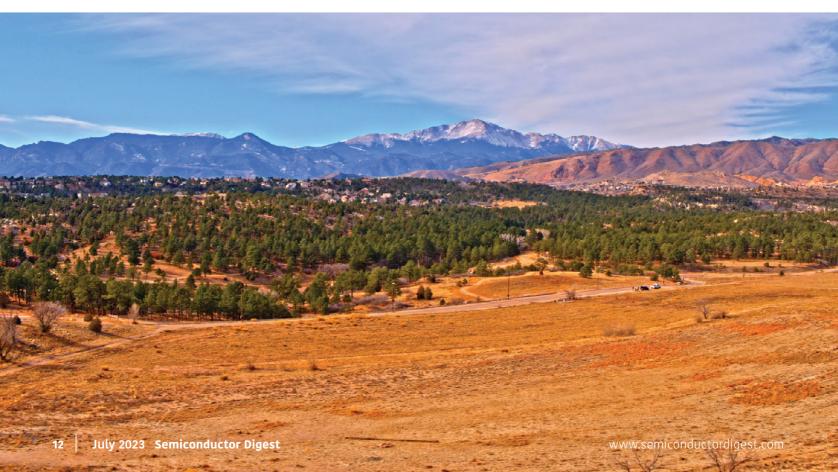

Entegris, Inc., a supplier of advanced materials and process solutions for the semiconductor and other high-technology industries, held a groundbreaking ceremony in June for its new manufacturing center of excellence in Colorado Springs, Colorado.

At the ceremony, Entegris President and Chief Executive Officer Bertrand Loy noted that the state-of-the-art facility in Colorado Springs will develop products critical to the manufacturing of semiconductors in the United States and around the world. The new leading-edge manufacturing center will serve the semiconductor industry, which is expected to grow to \$1 trillion by 2030. Entegris' commitment to innovation and investment in leading-edge manufacturing and supply chain operations will strongly position Entegris — and its customers — for success, and further bolster Colorado's and the U.S.'s position as a technology,

manufacturing, and innovation leader across the semiconductor ecosystem.

The new campus, which is targeted to begin initial commercial operation in early 2025, will be built in phases. The 100,000-square-foot facility to be built in the initial phase will support production for Entegris' Microcontamination Control (MC) and Advanced Materials Handling (AMH) divisions. Upon completion, the facility will increase production capabilities for Entegris' most advanced products for filtration and purification as well as wafer carriers, also known as Front-Opening-Unified Pods (FOUPs). The center of excellence will play an important role in the Colorado Springs community and has the potential to create approximately 600 new jobs over several years. Entegris continues to expect to invest approximately \$600 million in phases over several years in the facility and is looking forward to working with the city, county, and state to integrate

the site and surrounding land into the community in a way that preserves the natural beauty of Colorado Springs.

"The start of construction of our new world-class facility in Colorado Springs represents an important milestone for Entegris," Loy said. "The semiconductor manufacturing industry is set to expand in the United States following the passage of the CHIPS and Science Act, and Entegris' manufacturing center of excellence will enable our organization to play a meaningful role in this important effort. With our large stateof-the-art facility, we will help shorten the supply chain and more efficiently meet the growing needs of domestic manufacturers. We are pleased to have found an innovative and competitive home in Colorado Springs, and we look forward to building on our 30-year history in the region while enhancing our leadership position in the semiconductor ecosystem." 50

### **Efabless Reveals Winners of AI-Generated Silicon Design Challenge**

Efabless Corporation, the creator platform for chips, announced the winners of its AI Generated Open-Source Silicon Design Challenge. The challenge invited participants to use generative AI to design and tapeout an open-source silicon chip and to do so in three weeks. The wide range of participants and the variety of innovative designs showed how generative AI can accelerate and democratize innovation in chips.

The first-place winner of the contest, by the slimmest of margins, is QTCore-C1 by Hammond Pearce at New York University. The design is a co-processor that can be used for many applications, such as predictable-time I/O state machines for PIO functions as seen on some microcontrollers developed using the Chip-Chat methodology that the NYU team has published.

**The second-place winner of the contest** is Cyberrio by Xinze Wang, Guohua Yin, and Yifei Zhu at Tsinghua-Berkeley Shenzhen Institute. This design is a RISC-V CPU, implemented with Verilog code produced via a series of prompts given to ChatGPT-4.

The third-place winner of the contest is Asma Mohsin at Rapid Silicon. The design is a Model Predictive Control (MPC) that is used to predict future behavior and optimize control actions for a regulator control circuit provided in MATLAB code to ChatGPT-4 and then implemented with prompts in Verilog.

The winners and all the participants successfully demonstrated how tools such as ChatGPT, Bard and others can revolutionize chip design by automating many of the tedious tasks involved in the development process. Contestants have used these AI tools and others to generate Verilog code from natural language prompts, which they then implemented on the Efabless chipIgnite platform using the OpenLane open-source design flow. The contestants ranged from industry experts to people who had never before designed a chip. None of the winners had ever used the OpenLane Flow before.

Winning designs were selected by a panel of industry-respected judges who used pre-determined criteria, including design completeness, documentation, technical merit, and community interest. Efabless will now fabricate the three winning designs on its chipIgnite shuttle with the winners receiving packaged parts and evaluation boards – a value of \$9,750. In addition, the other participants with qualifying designs will receive a free evaluation board and one of the winning AI-generated chips.

"I would like to congratulate the winners for creating such impressive designs in such a short amount of time," said Mike Wishart, CEO of Efabless. "We were struck by the enthusiasm and collaborative participation of the community and the tremendous learning that was achieved by everyone involved. We look forward to our role in facilitating this innovation by providing a forum for learning and a platform to drive AI-assisted development from idea to silicon."

Efabless will soon release information about the second AI-Generated Design Challenge. The challenge will take place over the summer, with tapeouts expected in September. 50

### ROBUST HERMETIC BIMETAL COMPONENTS

Stainless Steel — EXW Bond-Line — Aluminum —

#### Demountable Bimetal Compone

- Stainless face/Aluminum body • CF Flanges

- Face Seal Fittings

All Welded Bimetallic Transitions

Tube and Pipe

#### **Custom Designs**

#### Industries

• Medical • Thin Film • Cryogenics • Aerospace

info@atlasuhv.com

www.atlasuhv.com

### Quantum-Si Debuts New HQ in Branford, Connecticut

Quantum-Si- Inc. officially debuted its new 29,420 square-foot headquarters in Branford, Connecticut. The new facility extends the company's decade long history in Connecticut, and includes a 7-year lease which will keep Quantum-Si in Branford at least through 2029. The official ribbon cutting, hosted on June 6, featured remarks from Quantum-Si Chief Executive Officer, Jeff Hawkins; Quantum-Si founder Jonathan Rothberg, PhD.; and special guests Governor Ned Lamont, US Senator Richard Blumenthal (D-CT), and Alexandra Daum, the Commissioner of the Connecticut Department of Economic and Community Development (DECD).

The new facility is located at 29 Business Park Drive in Branford, Connecticut, and provides the resources necessary for increased operational scale, development, and collaboration. This milestone represents Quantum-Si's anticipated growth trajectory and ability to support customers and partners using Platinum, the world's first next-generation single-molecule protein sequencing platform.

"The cities of Branford and Guilford, and State of Connecticut have been incredible partners to Quantum-Si since our founding. Our company's roots are here, our relationships are here, and we want to continue building a world-class company here." said Quantum-Si's Chief Executive Officer, Jeff Hawkins. "Our new headquarters reflects the company's ongoing commitment to job opportunities and innovation alongside the local community. We believe New Haven County is the perfect strategic location to attract world-class scientific talent as we seek to grow our teams. We look forward to leading the expansion of the life sciences industry in Connecticut."

"We have a truly transformative product on the market in Platinum, the next-generation protein sequencer, a leadership bench of highly experienced executives, and now we have the facilities to scale alongside that growth" said Dr. Jonathan Rothberg, Founder and Chairman of Quantum-Si. "Next-generation protein sequencing will be critical for the discovery of a new wave of precision therapies, and I am proud to see this work being done in the community I call home."

Platinum is the world's first next-generation single-molecule protein sequencing platform that uses proprietary recognizers to identify proteins and amino acids using kinetic binding signatures. Its elegant design and simple workflow enables broadscale access to proteomic data, for every scientist, everywhere, making it a ground breaking platform for the future of proteomics research. With its small benchtop design and low pricepoint, Platinum is poised to accelerate breakthroughs across scientific disciplines, from drug discovery to biotech, and help people live healthier and longer lives. 50

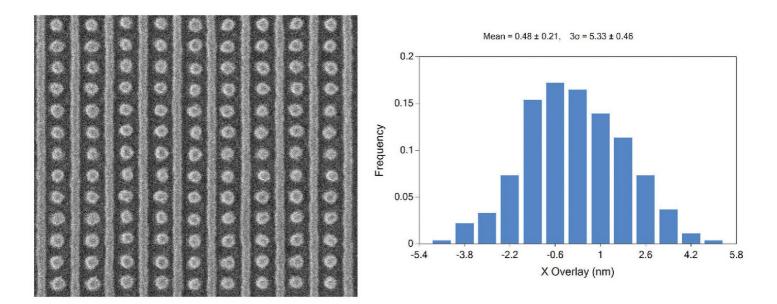

### Fractilia Adds Overlay Metrology Capability to Stochastics Control Solutions

Fractilia, the leader in stochastics metrology and control solutions for advanced semiconductor manufacturing, introduced the Fractilia Overlay Package, an optional offering that adds critical new overlay measurement and analysis capabilities to Fractilia's MetroLER<sup>™</sup> and FAME<sup>™</sup> products. Fractilia's products, which combine the company's patented Fractilia Inverse Linescan Model (FILM<sup>™</sup>) technology with true computational metrology, are the only proven fab solutions that provide highly accurate and precise

measurements of all major stochastic effects – the single largest source of patterning errors at advanced nodes. Fractilia is currently engaged with multiple leading chip manufacturers in analyzing their SEM-based overlay data with the new Fractilia Overlay Package.

In semiconductor manufacturing, overlay is the precise placement of each patterned layer relative to a previous layer to ensure electrical contact and produce a functioning device. Optical-based metrology tools have traditionally been used by chip manufacturers to measure and control this pattern overlay, which is essential to producing high-yielding and high-performing semiconductor devices. These measurements are made on special targets in the scribe line rather than in the device itself. As feature sizes of chips continue to shrink and as stochastic variability has increased with the adoption of EUV patterning, there is a growing offset between what is measured in the scribe line and what is happening in the device. As a result,

The Fractilia Overlay Package measures SEM overlay between features and calculates the overlay distributions, across-wafer variations, and much more. Source: Fractilia.

interest is growing in the use of SEM tools to measure overlay due to their higher resolution and precision compared to optical tools. However, SEMs introduce noise in the SEM image, which can be easily confused with stochastic variability on the wafer.

"SEM-based overlay measurements are increasingly being used to improve advanced patterning process control, but they are influenced by the same random and systematic SEM errors that affect other stochastics measurements," stated Fractilia CTO Chris Mack. "Fractilia is unparalleled in measuring and subtracting out SEM noise through our proven FILM technology, and as a result, our customers are turning to Fractilia to help them apply our technology to improve the accuracy of their SEM overlay measurements. In addition, by combining SEM stochastics measurements with optical overlay measurements through our Fractilia Overlay Package, we believe that we not only can improve SEM overlay metrology accuracy, but also provide better lot dispositioning and correctables, which in turn can improve patterning control and reduce non-zero offset (NZO) or its variability."

### "Unbiased" measurements provide more accurate description of what's on the wafer

Fractilia's FAME portfolio of solutions uses a proprietary and unique physics-based SEM modeling and data analysis approach that measures and subtracts the random and systematic errors from SEM images to provide measurements of what is on the wafer rather than what is on the images. FAME measures all major stochastic effects simultaneously, including line-edge roughness (LER) / linewidth roughness (LWR), local CD uniformity (LCDU), local edge placement error (LEPE), and stochastic defects, as well as provides CD measurements. It provides the highest signal-to-noise edge detection in the industry (up to 5x higher signal-to-noise ratio than other solutions), and extracts more than 30x more data from each SEM image.

thermal engineering, our team has supplied heating solutions to manufacturers of high-purity silicon, silicon wafers, and other semiconductor products across the globe. With the new Fractilia Overlay Package, Fractilia adds highly accurate SEM-based overlay measurements, including their stochastic properties, on top of its existing measurement capabilities. Fractilia's products have been adopted throughout the industry by dozens of companies, including leading semiconductor manufacturers, equipment companies, materials suppliers and research organizations. 50

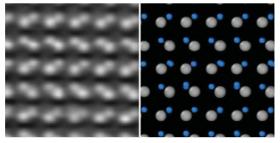

### Novel Ferroelectrics for More Efficient Microelectronics

As computational energy usage continues to grow, it is on pace to potentially become the leading source of energy consumption in this century. Memory and logic are physically separated in most modern computers, and therefore the interaction between these two components is very energy intensive in accessing, manipulating, and re-storing data. A team of researchers from Carnegie Mellon University and Penn State University is exploring materials that could possibly lead to the integration of the memory directly on top of the transistor. By changing the architecture of the microcircuit, processors could be much more efficient and consume less energy. In addition to creating proximity between these components, the nonvolatile materials studied have the potential to eliminate the need for computer memory systems to be refreshed regularly.

Their recent work published in *Science* explores materials that are ferroelectric, or have a spontaneous electric polarization that can be reversed by the application of an external electric field. Recently discovered wurtzite

In-situ experimental STEM images (left panel) and first-principles calculation prediction (right panel) France.

ferroelectrics, which are mainly composed of materials that are already incorporated in semiconductor technology for integrated circuits, allow for the integration of new power-efficient devices for applications such as non-volatile memory, electro-optics, and energy harvesting. One of the biggest challenges of wurtzite ferroelectrics is that the gap between the electric fields required for operation and the breakdown field is very small.

"Significant efforts are devoted to increasing this margin, which demands a thorough understanding of the effect of films' composition, structure, and architecture on the polarization switching ability at practical electric fields," said Carnegie Mellon post-doctoral researcher Sebastian Calderon, who is the lead author of the paper.

The two institutions were brought together to collaborate on this study through the Center for 3D Ferroelectric Microelectronics (3DFeM), which is an Energy Frontier Research Center

> (EFRC) program led by Penn State University through funding from the U.S. Department of Energy's (DOE) office of Basic Energy Science (BES).

Carnegie Mellon's materials science and engineering department, led by Professor Elizabeth Dickey, was tapped for this project because of its background in studying the role of the

structure of materials in the functional properties at very small scales through electron microscopy.

"Professor Dickey's group brings a particular topical expertise in measuring the structure of these materials at very small length scales, as well as a focus on the particular electronic materials of interest of this project," said Jon-Paul Maria, professor of Materials Science and Engineering at Penn State University.

Together, the research team designed an experiment combining the strong expertise of both institutions on the synthesis, characterization and theoretical modeling of wurtzite ferroelectrics. By observing and quantifying real-time polarization switching using scanning transmission electron microscopy (STEM), the study resulted in a fundamental understanding of how such novel ferroelectric materials switch at the atomic level. As research in this area progresses, the goal is to scale the materials to a size in which they can be used in modern microelectronics. SE

# HYBRID AMHS FOUP/SMIF OHT

For more information, visit our website by scanning the QR Code or email us at sales@stratusauto.com

Copyright © 2023. Stratus Automation Sdn Bhd. All rights reserved.

# **ATE** is *Our* Business

**ElevATE:** High-Density, Low-Power Semiconductor Test Solutions

www.elevatesemi.com

As technology advances at an unprecedented pace, the demand for semiconductor test solutions surges. Elevate is dedicated to addressing the challenges of power efficiency, density, speed, and voltage. Are you prepared to put your upcoming product roadmap to the test?

### Test

### Challenges in Testing Semiconductors with 5nm and Smaller Process Geometries

Elevate Semiconductor's latest DPS/PMU products offer improved architectures to maximize power efficiency, while providing high channel counts and DC accuracy necessary to test tomorrow's state-of-the-art devices.

VER RECENT YEARS, THE SEMIconductor market has seen considerable growth, driven largely by the advancements in AI, 5G, HPC, Edge Computing, and autonomous vehicles sectors. This has led to a surge in demand for new fabs capable of supporting increasingly small process geometries.

Current and projected fab investments indicate a trend towards sub-5nm and in some instances, sub-2nm process nodes. Driven by the CHIPS Act and other non-US funding, more than \$150 billion worth of fabs are presently under development, with industry leaders such as Samsung and TSMC opening fabs in the US, and Intel also investing in European fabs.

Next-generation products, designed with these smaller geometries, are also under development. Examples include the next-generation Apple iPhone 15 Pro/Ultra 3nm processor and Nvidia's H100 GPU/AI 4nm processor.

However, these advancements bring new complexities. Testing semiconductors with process nodes of 5nm or smaller is a challenging task. Manufacturers are in pursuit of future-proof test solutions that ensure optimal yield and quality while also controlling costs.

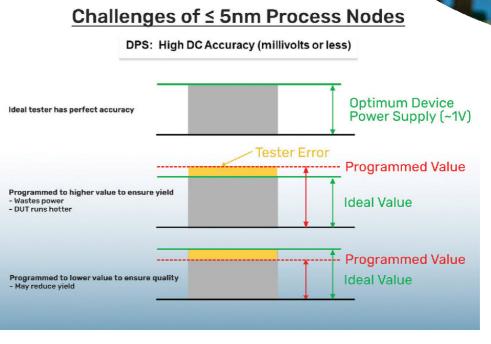

Figure 1. High DC Accuracy of 1 millivolt or less is often required.

However, as semiconductors become smaller with more gates and more complexity, testing takes longer. Without improvements in testing, these costs can become the largest part of a company's cost of goods.

#### Testing challenges of sub-5nm process nodes

Components designed with sub-5nm process nodes demand reduced

operating voltages (less than 1 volt) while drawing 1000s of amps (**FIGURE 1**). These tiny geometries operate at faster speeds and are densely packed with features and functionalities. The chips can be large in format and have pin counts exceeding 1000, all of which need to be tested before final production. This can cause considerable issues. In the case of large AI processors, it's impossible to conduct a

full test all at once with current testing technology. The only feasible option is to partially test them in series, one section at a time.

In order to test these sophisticated chips with so many pins, the test solutions need to have numerous channels, positioned as closely as possible without causing overheating. Enhanced power efficiency is not only necessary for power savings but also to enable increased density. With operating voltages at 1 volt or less, high DC accuracy of 1 millivolt or less is essential to provide the proper voltage to the device under test (DUT).

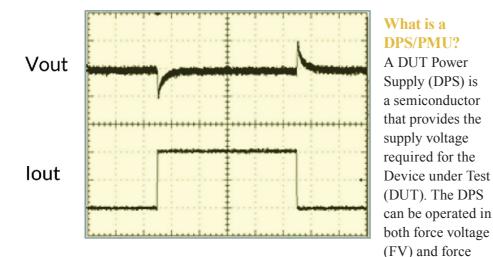

Other requirements include a faster load transient response to avoid potential yield issues caused by voltage droop (**FIGURE 2**). typical power supply as well as the capability to read back and measure the voltage and current. A Parametric Measurement Unit (PMU) and a DPS are alike, but the DPS has higher current capabilities than the PMU. A Per-pin PMU (PPMU) architecture significantly reduces test time as every DUT pin can be tested simultaneously.

current (FI) mode

and has functionality similar to a

#### DPS/PMU Solutions for Testing ≤5nm process nodes from Elevate Semiconductor

Elevate Semiconductor, established in 2012, is dedicated to developing cutting-edge technology that facilitates the next generation of testing in the semiconductor industry. The company offers a comprehensive range of

Device Power Supply (DPS) and Parametric Measurement Unit (PMU) products, designed to last and keep up with technological advancements (FIGURE 3).

Elevate Semiconductor's latest DPS/ PMU products offer improved architectures to maximize power efficiency, while providing high channel counts and DC accuracy necessary to test tomorrow's state-of-the-art devices.

Unique in the industry, Elevate Semiconductor focuses solely on testing. Their test solutions include a full range of DPS/PMU, Pin Electronics, and VI products. The company's solutions are designed to be low-power

Figure 3. Elevate next-gen D.PS/PMU.

and high-density, aiming to reduce testing costs (through parallelization).

To learn more about Elevate Semiconductor and their DPS/PMU solutions, go to https://elevatesemi.com/engage/

Tim Bakken, Elevate Semiconductor Vice President of Global Sales stated: "By actively engaging and collaborating with our clients, Elevate fosters a deep understanding of the problems our customers are trying to solve. This collaborative approach drives our ability to develop effective solutions for every challenge. Our extensive portfolio includes a wide range of offerings, from standard solutions to semi-custom and full-custom options. With our customer-centric focus, collaborative mindset, and diverse offering. Elevate Semiconductor is committed to delivering exceptional products and service to our valued customers. 50

### Trends

### The State of the Semiconductor Industry 2023

PETE SINGER, Editor-in-Chief

New approaches will be required to address challenges associated with energy efficiency, the explosion of AI and emerging automotive applications.

MID A BACKDROP OF SEVERAL SEVERE global crises - war, climate change, an aging population and supply chain disruption, plus the need for better mobility, reliable energy, healthcare - the role that semiconductors play on the world stage has never been more important. "It is clear that complex deep tech innovations will be essential to address these phenomenal challenges our planet and our society is facing," said Luc Van den hove, president and CEO of imec, speaking at the consortiums recent ITF World meeting, held May 17-18, in Antwerp, Belgium. Other presenters included Jensen Huang, president, CEO and Member of the Board of Directors at NVIDIA, Mark Papermaster, executive vice president and chief technology officer of technology

and engineering at AMD, Jaihyuk Song, corporate president and CTO of Samsung Electronics' Device Solutions Business, and Christophe Fouquet, CBO & Board of Management at ASML. In this article, we summarize their insights into the major trends, challenges and possible solutions in the years ahead for the semiconductor industry.

#### More data than stars

There are many drivers of semiconductor consumption — cloud computing, 5G, IoT, automotive, mobile, AR/VR, phones, etc. — and, in just the last year,

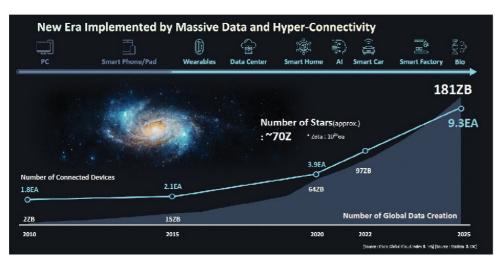

**Figure 1.** The world's data creation has already exceed the estimated number of stars in the universe. *Source: Samsung, ITF World.*

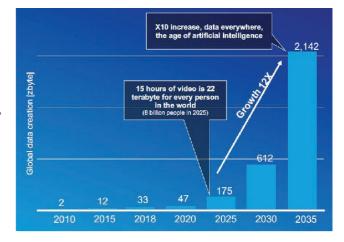

**Figure 2.** Data creation is expected to increase 12X in the next decade. *Source: ASML, ITF World.*

generative artificial intelligence and ChatGBT. The general consensus is that the market for semiconductors will reach \$1Trillion by 2030, practically double was it is today. To achieve this, billions of dollars in investments in new factories and research centers have been announced over the last year, spurred on by billions in government incentives in the U.S. (The CHIPS Act), Europe, Japan, Korea and China. Major efforts are underway to supply the workforce that will be needed.

One of the most useful ways of looking at semiconductor demand is the amount of data being generated, which of course, must be collected, analyzed and acted upon. "The amount of data generated each year is exploding," said Samsung's Song. "It is more than two and a half times the number of stars in

SMART

SMART MOBILITY ഹ്രം

> SMART MEDTECH ъb

### Connecting Semiconductors and Electronics

WORKFORCE DEVELOPMENT

> Global ADVOCACY

#### About SEMI:

SEMI connects more than 2,500 member companies and 1.3 million professionals worldwide to advance the technology and business of electronics design and manufacturing. The breadth and depth of our events, programs and services help members accelerate innovation and collaboration on the toughest challenges to growth.

Electronic System Design Alliance

Sustainability

MARKET INTELLIGENCE TEAM

1000 +STANDARDS

THOUGHT LEADERSHIP

SEMICON

TECH COMMUNITIES

SEMI UNIVERSITY

Cyber Security the entire universe currently estimated by space scientists."

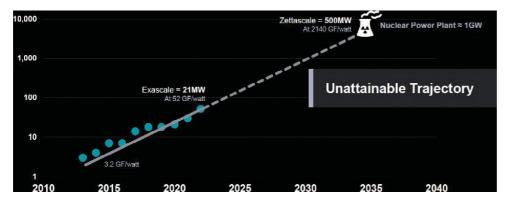

This trend is illustrated in **FIGURES 1** and **2.** AMD's Papermaster noted that if we stay on the same pace, the power needed for supercomputer installation will approach that of a nuclear power plant (**FIGURE 3**). "That's a pretty scary data point, and what it really tells you is that we are hitting absolute limits of energy consumption," he said. The solution: changing the way computing is done to bring the memory closer to the CPU, and new more energy efficient chip designs and architectures.

"It will take a holistic approach to bend the curve, to be able to improve our rate of energy efficiency," Papermaster said. "We have to expand

#### The explosion of AI

Van den hove said the fast growth of generative AI is driven by three primary factors: Advancement in AI models, access to large amounts of data, and massively increased compute power. "The compute needs for AI are literally exploding, and we are just at the beginning," he said. "In order to generate this required compute power in a sustainable way, we will need drastically more performant devices and systems."

Nvidia's Huang noted that, in the past decade, the scale of deep learning has increased by a million times. "Then, ChatGPT arrived.. the AI heard around the world," he said. "ChatGPT, a generative pre-trained transformer, is a large

**Figure 3.** Green500 supercomputer GFLOPS/Watt and projection. The Green500 is a biannual ranking of supercomputers in terms of energy efficiency. *Source: AMD, ITF World.*

the sphere of co-operative and more co-design optimizations across the stack.. and really drive system level implementations. We have to think differently, and really leverage innovation. If you look at the way that we've always designed — focusing on silos and then putting that sum of parts together — it simply can't bend the curve," he said.

AI is set to worsen the problem. "AI, with the large language models and the energy needed to train, is going to actually grow that rate and pace of energy consumption," Papermaster said, noting billions of parameters are used to today to train models such as ChatGBT3, and "it's heading to trillions of parameters." language model with hundreds of billions of parameters trained on trillions of words and sentences. It has learned the representation of human language and can generate text. ChatGPT is revolutionary due to its ease of use and incredible capabilities. It's a glimpse into the future of computers that understand any programming language and perform a broad range of tasks."

Huang noted that, already, over a thousand generative AI startups are inventing new applications. Tabnine, for example, is a contextual code assistant that helps complete lines of code or generate entire functions from a prompt description. It can program in multiple popular languages from JavaScript and Python to Rust, GO, and BASH.

Runway uses generative AI to create and edit images and videos. Its production quality is so impressive that several Oscar nominated films have used it. With Runway's, generative AI, anyone can tell stories through pictures and video.

Insilico Medicine uses generative AI to create a candidate drug in one third a time, and one tenth the cost of traditional methods, which usually take over four years and cost around \$500 million. Insilico Medicine is used by over 20 pharmaceutical companies.

"The market impact of perception AI is already significant," Huang said. "The impact of generative AI will be much bigger. The remarkable ease of use allowed ChatGPT to reach over 100 million users in just a few months, making it the fastest growing application in history." He said that every form of information will be understood and enhanced by generative AI, "from human language, music, pictures, video and 3D to genes, proteins, and chemicals." The content on 200 million websites will be personalized and generated by AI, he said, and billions of customer service calls will be automated by AI. Generative AI will also assist 25 million software developers and hundreds of millions of creators.

What is the next wave of AI? Huang said it's "Embodied AI" which refers to intelligent systems that can understand, reason about, and interact with the physical world. Examples include robotics, autonomous vehicles, and even chatbots that are smarter because they understand the physical world.

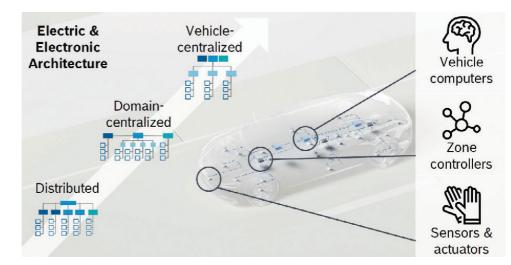

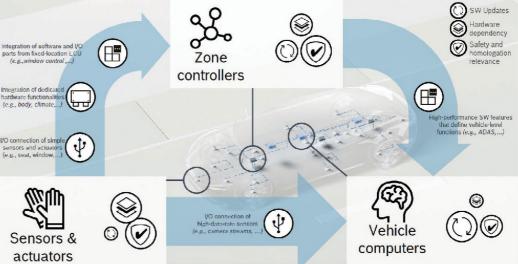

#### **Automotive requirements**

Automotive applications are another hot driver of semiconductor technology, including electric vehicles (EVs) and autonomous driving. In addition to advanced battery management systems, the future car requires next generation sensing,

# 45th EOS/ESD SYMPOSIUM AND EXHIBITS

October 1-6, 2023 Riverside Convention Center Riverside, CA

### Program and registration details updating at: https://esda.events/

Our program is packed! While we prepare for the full program, check out the incredible tutorials available this year and the deep discounts for registering early for the symposium!

Tutorials offered:

FC340: ESD Program Development and Assessment – ANSI/ESD S20.20 Seminar-Two days (\$1,710)

FC100: ESD Basics for the Program Manager (\$950)

FC101: How To's of In-Plant ESD Auditing and Evaluation Measurements (\$950)

DD/FC240: System Level ESD/EMI (Principles, Design Troubleshooting, & Demonstrations) - (\$585)

DD134: Fundamentals of ESD System Level (\$585) Symposium pricing:

ESDA Member: \$600 Changes to \$800.00 after Monday, July 24, 2023

ESDA Life Member Fee \$525.00 Changes to \$725.00 after Monday, July 24, 2023

Non-ESDA Member Fees \$700.00 Changes to \$800.00 after Monday, July 24, 2023

Membership discounts apply to current members as of May 31, 2023. Memberships processed after this date will not apply.

### Register at: https://cvent.me/G57zBw

combining multiple multispectral cameras and multiple radars, including short range and long range radars. "All these sensors will generate incredible amounts of data," Van den hove said. "To process this, our cars will need radically new compute architectures implementing massive amounts of AI running on powerful, centralized electronic control units. When evolving from current ADA systems towards increasing levels of autonomous driving, the required compute power is increasing exponentially. The electronic control units in the cars are actually quickly growing into what used to be a supercomputer performance level," he said.

The energy efficiency of these compute platforms will also become extremely important. "Power consumption will explode and could contribute to consuming up to even one third of the battery range when navigating in busy city centers," Van den hove said. "The chips needed for these ECUs will be among the most complex monolithic designs one can find and will be built using the most advanced silicon nodes."

He added that, while the semiconductor content in cars will increase tremendously leading to a growing semiconductor demand, the total number of globally produced cars is not increasing significantly. "Designing these ultra expensive compute systems on chip and optimizing them in a flexible way for specific markets like high-end and low-end markets is really not obvious," he said. "We will therefore need to optimize these compute architectures taking into account flexibility, complexity, energy efficiency, and affordability."

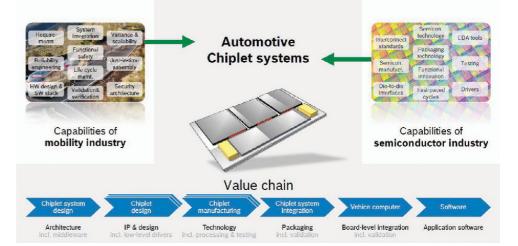

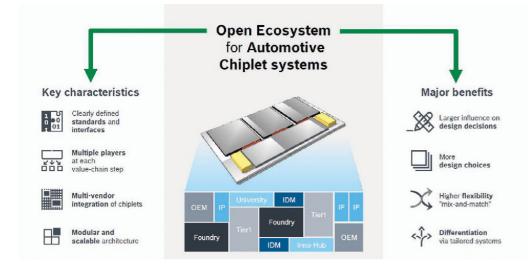

One approach that's gaining interest in this regard is chiplet-based designs, where the design is broken out into smaller pieces of silicon chiplets that are fused together using advanced heterogeneous integration techniques. "Using chiplets, ECUs can be configured in a more flexible way, allowing for high-end or low-end configurations without having to redesign the entire chip. It'll allow for the reuse of IP as the chips will be smaller, it'll provide better yield and reliability, which is essential for the auto industry," Van den hove said.

#### Moore's Law, 2D scaling, 3D stacking and chiplets

The semiconductor industry has enjoyed the benefits of 2D scaling, as defined by Moore's Law, for decades. As that type of scaling slows, alternative approaches, such as chip stacking and chiplets are coming into play. "We believe that Moore's law, as we traditionally know it, will still be essential. Indeed, feature-based scaling by reducing the dimension of our individual transistors is still one of the only techniques that provides true exponential complexity increase," Van den hove said.

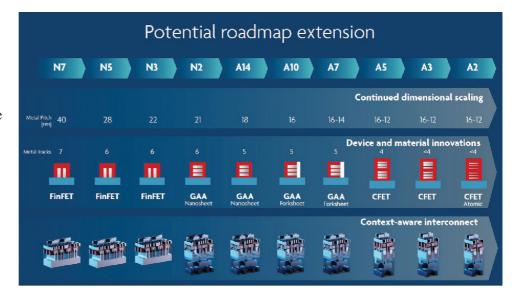

He showed imec's roadmap for the next decade (**FIGURE 4**), which includes the continued use of 2D scaling, as well as new technologies, such as forksheet transistors and complementary FET (CFET). In a CFET architecture, n- and pMOS devices are stacked on top of each other, allowing further maximization of the effective channel width. "We can enable continued scaling for many more generations by combining lithography-based scaling and the introduction of new interconnect schemes, new materials, and new device architectures, such as the CFET device," Van den hove said.

He also spoke of "walls" that may be difficult to get over. The power wall, where it becomes increasingly difficult to scale the power consumption per transistor, and the memory wall, defined by the delay between the time the CPU needs data from SRAM-based caches or DRAM, and the moment it can access it. "With a lot of AI workloads, it is getting harder to get data efficiently in and out of our processors. In fact, for specific AI workloads in high performance computers, in some cases processors are only active less than 3% of the time," he said. "Most of the time they're actually waiting for data, so we'll, therefore, need to reconsider memory system architecture."

Imec has also identified three other walls:

• The scaling wall: pure lithography-enabled scaling is slowing down. It is becoming increasingly difficult since individual structures of microchips and transistors are approaching the size of atoms, where

**Figure 4.** Imec's new roadmap includes the continued use of 2D scaling, as well as new technologies, such as forksheet transistors and complementary FET (CFET). *Source: imec, ITF World.*

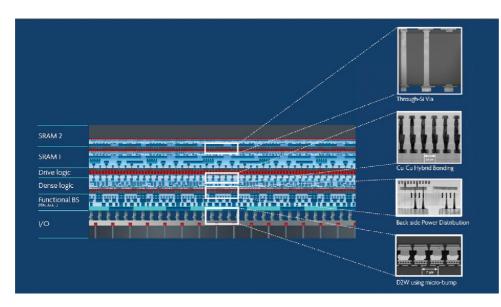

**Figure 5.** Advanced wafer stacking techniques could employ through-silicon via technology and copper-to-copper hybrid bonding to enable very high dense interconnects between the logic and the memory cache layers. *Source: imec, ITF World.*

quantum effects begin interfering with the operation of microchips.

- The sustainability wall: the manufacturing of semiconductor devices contributes to an increasing environmental footprint, including greenhouse gas and water, natural resources, and electricity consumption.

- The cost wall: obviously, chip manufacturing costs may explode with the complexity increase, together with the costs for design and process development.

Van den hove said the industry will need a wide portfolio of technology options that will allow for specific technology combinations for addressing specific workloads and system requirements. "Interposer chips and tiny silicon bridge interposers will allow for very fast connections between multiple core processor chiplets and 3D DRAM memories," he said.

Today, DRAM memories are typically built up as a 3D stack of layers, while the core processor chiplets are made using a single die, a monolithic 2D system of chip. "The next way to enable heterogeneous integration is to build up the advanced 2D processor die as a 3D stack of layers, splitting up the functionality across multiple layers. This can be done using advanced wafer stacking techniques such as by using through silicon via technology, copperto-copper hybrid bonding, enabling very high dense interconnects between the logic and the memory cache layers," Van den hove said. **FIGURE 5** illustrates how this might look in practice.

"We believe that this will be one of the ways to extend Moore's law much further than what we believe possible. We refer to this roadmap as CMOS2.0, realizing the next phase of Moore's law by using 3D stacking to enable further 2D scaling. 3D alone will bring us only linear complexity increase," said Van den hove.

Another issue is that the power consumption of advanced chips is increasing to a point where there are some limits on extracting the heat out of the chip. "It is clear that in order to enable such complex 2D, 3D stacked core processor architecture, we will need to address the heating problem and learn how to cool the chips more effectively. For this, we're developing innovative cooling systems, which can be fabricated using 3D printing techniques," Van den hove said. This direct liquid jet impingement cooling results in much higher heat extraction efficiencies, up to five times better than the current state-of-the-art.

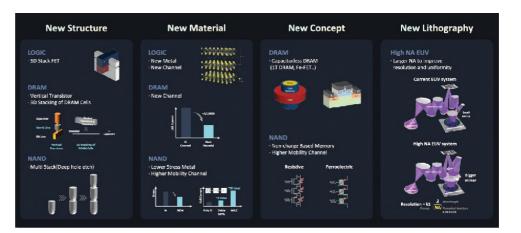

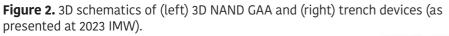

Samsung's Song identified trends specifically related to logic, DRAM and NAND device structures. In logic, to resolve the problem of cell height scaling, he said Samsung is developing backside interconnects. "In addition, innovation in structure and materials such as channel materials with optimum layer thickness can have excellent gate controllability compared to silicon channels," he said (see **FIGURE 6**).

In DRAM, to address the issue of lateral scaling, Samsung is studying a vertical channel stacked 3-D structure that Song said is very different from the existing 2-D structure. "We are also trying to introduce all lowleakage channel material, not the silicon channel that has been used so far leakage current control," he said. "In order to solve the cell capacitor problem, we are making approach to overcome the limitations by studying a new concept of DRAM without a capacitor."

In NAND, technologies such as multi-stack will continue to be developed. "New materials would be required to overcome mechanical stress or sensing margin. And new concepts of device development that can lower operating voltage would be required to further shrink up the unit device size," he said. "To increase the resolution and uniformity of EUV, the high-NA EUV technology, which uses larger mirrors is also needed."

### The need for innovation and collaboration

"In order to continue to develop the digital transformation era, the technology for storing and processing such big data requires a new era of development, and there is a constant need for innovation in the semiconductor industry to make this possible," Song said. Continued on page 35

### Sustainability

### Carbon Capture, Utilization, and Storage Technologies' Role in Fighting Global Warming

CHRIS JONES, Edwards Vacuum

Carbon capture, utilization, and storage (or sequestration) (CCUS) refers to various technologies that capture carbon dioxide at a source or from the atmosphere (direct air capture) and then either use it or store it so that it does not contribute to warming the planet.

There is broad consensus within the scientific community that human-generated greenhouse gas (GHG) emissions are causing global warming. If we can emit them, might we capture and remove them? The answer is yes, though perhaps not as easily. But capture them we can, and

we are. The real questions are, can we do it fast enough and big enough to make a difference, and can we afford it, in terms of dollars and energy? These questions fall within the purview of geoengineering, the third leg (in addition to mitigation and adaptation) of the framework within which most

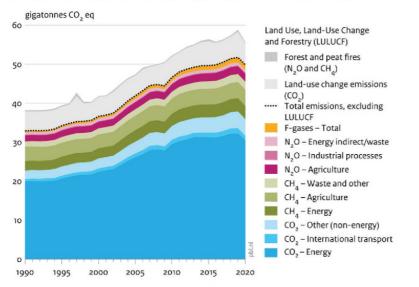

Global greenhouse gas emissions, per type of gas and source, including LULUCF

Source:  $CO_{2}$ ,  $CH_{q}$ , NQ, F-gases excl. land-use change: EDGAR v6.0 FT2020; incl.  $CH_{q}$  and  $N_{2}O$  from savannah frires: FAO 2021; GHG from land-use change:  $CO_{2}$  from Global Carbon Budget (GCB 2020);  $CH_{q}$  and  $N_{2}O$  from forest and peat fires: GFED4.15 2021 Note:  $CO_{2}$  eq with GWPs from IPCC AR4

**Figure 1.** Global GHG emissions by type of gas and source. CO2 from energy production is by far the largest contributor. (https://www.pbl.nl/en/publications/trends-in-global-co2-and-total-greenhouse-gas-emissions-2021-summary-report)

experts discuss as a response to climate change. Carbon capture, utilization, and storage (or sequestration) (CCUS) refers to various technologies that capture carbon dioxide at a source or from the atmosphere (direct air capture) and then either use it or store it so that it does not contribute to warming the planet.

We are currently emitting about 55 gigatons of GHG (CO, equivalent  $-CO_2e$ ) per year.  $CO_2$  is the major component, but there are also major contributions from other gases (FIGURE 1). Methane (CH<sub>4</sub>) and nitrous oxide  $(N_2O)$  emissions are smaller in volume but have much greater global warming potentials, ton for ton, over a 100-year period (GWP-100), 27.9X and 273X the GWP-100 of CO<sub>2</sub> (respectively). Fluorinated gases also contribute significantly to warming with GWP-100 as much as 25,000X CO<sub>2</sub>. At the current rate of emission, we will exceed the budget required to restrict warming to less than 1.5°C before 2030.

In the 2015 Paris Agreement most countries in the world agreed to reduce GHG emissions enough to hold the increase in the global average temperature to well below 2°C above pre-industrial levels and pursue efforts to limit the temperature increase to 1.5°C above pre-industrial levels. In 2018 the Intergovernmental Panel on Climate Change (IPCC) warned that we would see substantial impacts if the temperature increased by more than 1.5°C. The Science Based Targets Initiative (SBTi) establishes reduction protocols and standards for companies to use

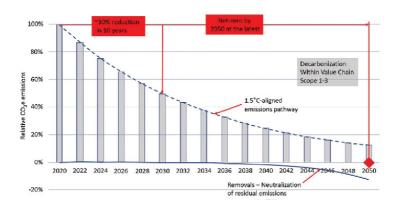

**Figure 2.** Reductions in GHG emissions needed to limit warming to 1.5°C.

to measure GHG emissions against targets that will limit warming to  $1.5^{\circ}$ C (**FIGURE 2**). To do so we must approximately halve emissions each decade, i.e., 50% by 2030, then another 50% by 2040, before achieving net-zero emissions by 2050. Emissions from some sectors, such as air transport, may be difficult or impossible to eliminate. CCUS provides a means to remove residual CO<sub>2</sub> emissions that cannot be completely eliminated, especially as we come closer to the end of the journey where progress from reductions becomes harder to realize.

There has been accelerating growth in CCUS efforts around the world over the last few years. Early results from some innovative technologies are encouraging, and it may be that CCUS will play a larger role in the fight against warming than originally suggested. FIGURE 3 summarizes CCUS projects in development or operation worldwide as of September 2021. Both the number of projects and their geographical distribution are increasing. Net maximum capacity (not actual operating capacity) was 175 MMT per year. That is a respectable number, but it is less than 0.4% of global emissions.

#### Capture

Carbon capture can contribute in several ways to our efforts to achieve net-zero emissions. Most immediately, it can reduce emissions from fossil-fuel based electrical power generation that accounts for more than 60% of emissions in the U.S. We are making progress in developing green energy sources, including solar, wind, nuclear and geothermal, but capturing carbon from fossil fuel combustion would allow a slower phase out of fossil fuels while still meeting emission targets. In so doing it would ease the transitional impact on employment in the energy industry and avoid the cost of retiring fossil fuel facilities and infrastructure prematurely.

In other industries, carbon emissions come from the process itself. Examples include the production of cement and the manufacture of iron and steel. In the first step of the cement process, limestone (primarily calcium carbonate) is heated to form calcium oxide (lime) and  $CO_2$ . Although new cement formulations can reduce process emissions, capturing the carbon from this step is the only practical way to reach net-zero in this sector. Likewise, the initial step in the manufacture of steel involves the reduction of iron in iron ore (primarily iron oxide) by exposing it to heat and carbon monoxide, producing metallic iron and  $CO_2$ . There are other ways to reduce iron, such as

using hydrogen instead of carbon monoxide as the reducing agent, but they are not yet widely used. Both cement and iron/steel making require high temperatures that are usually supplied by fossil fuel combustion.

The third option is capturing and storing carbon directly from the atmosphere. The primary challenge for direct air capture is the very low concentration of  $CO_2$  in the atmosphere, which makes the capture process energy intensive. Unless the energy it uses is renewable, direct air capture can add more  $CO_2$  than it removes. Still, it is the only option, of the three discussed here, that can actually take  $CO_2$  out of the atmosphere. Bioenergy with carbon capture and

<figure>

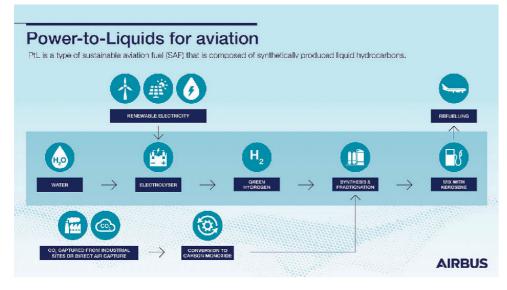

Figure 4. Energy pathway for producing sustainable aviation fuel

storage (BECCS) refers to energy pathways that capture and store biogenic carbon. For example, in the production of ethanol from corn, the growing corn captures CO<sub>2</sub> directly from the atmosphere and converts it to carbohydrates. A fermentation process converts the carbohydrates to ethanol and CO<sub>2</sub>. The ethanol may be added to fuels and returned to the atmosphere when it is burned, or it may serve as feedstock for other industrial processes. The CO<sub>2</sub> generated by fermentation is highly concentrated and, therefore, easily captured and stored in geological formations. Other, more complicated BECCS processes show great promise for use in energy generation and carbon intensive industrial processes like cement and steel production. In all cases the energy produced is carbon neutral, coming from and returning to the atmosphere, and carbon stored or incorporated in long-lived products is removed from the atmosphere, i.e., carbon negative.

#### Utilization

Of course, the value of carbon capture in reducing global warming depends on what is done with the carbon after it is captured. One option is to use it in place of carbon from fossil sources. Some uses keep the carbon out of the atmosphere for only a short time, such as synthetic jet fuel (**FIGURE 4**). Still. If the carbon was extracted from the atmosphere to begin with, using renewable energy, then the net carbon contribution when it is burned can still be zero. It becomes a way to make green energy available to industries like aviation where finding a substitute for hydrocarbon fuels is challenging.

Other uses, such as building materials, retain carbon for a very long time. Synthetic aggregates made by mineral carbonation can provide essentially permanent storage of CO2. The carbon dioxide may come from flue gas or other pure streams. Synthetic aggregates can also be used to dispose of industrial wastes such as fly ash, steel slag, and cement kiln dust. Concrete is 60% to 80% mineral aggregate. In traditional concrete, the aggregates are mixed with water and cement. The water converts the cement to interlocking crystals that bind the concrete together. CO<sub>2</sub>-cured concrete uses non-traditional cements that cure when mixed with  $CO_2$ . This is a mature technology that can be cost competitive with traditional concrete, though it is currently used primarily for precast concrete blocks.

#### Storage

Storage in geological formations, such as oil and gas reservoirs, unmineable

coal seams, and deep saline reservoirs, is generally considered to be safe and secure when the storage facility is properly sited and operated. In nature, CO<sub>2</sub> remains trapped in these formations for millions of years. We have extensive experience storing CO<sub>2</sub> underground, with industrial scale projects dating back to the 1970's. Oil and gas producers use CO<sub>2</sub> injection in advanced recovery techniques to force the last bit of oil from a deposit. This should not be taken as license to continue emitting GHG with the thought that it can simply be put back into the ground where it came from. Though known potential geological storage capacity is large, it is not unlimited. The ultimate solution remains the reduction of emissions

#### Semiconductor industry