# **SOC 8-Channel DPS**

#### **Vesuvius**

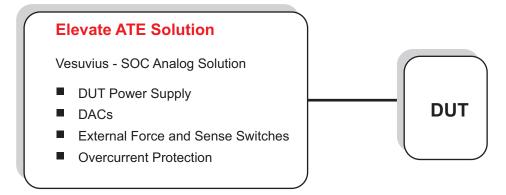

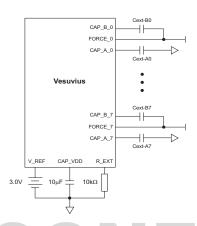

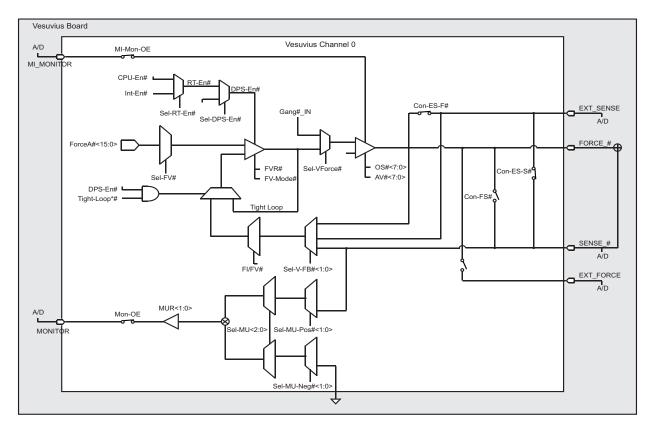

Vesuvius is a highly integrated System-on-a-Chip (SOC) Device Under Test (DUT) power supply solution incorporating 8 independent DUT Power Supply (DPS) units.

The interface, the control, and the I/O are digital; all analog circuitry is inside the chip. For most tester applications, no additional analog hardware needs to be developed or used on a per channel basis.

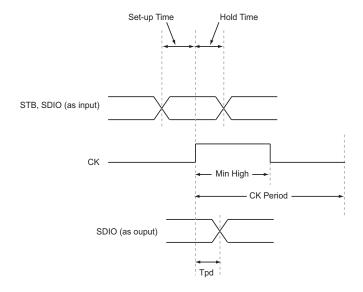

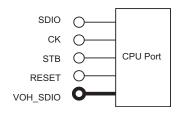

All configuration setup and the writing to and reading back of the internal registers are controlled through the 3-bit serial data CPU port. The CPU port is typically used to setup the operating conditions of each channel prior to executing a test, or to change modes during a test.

An internal register chart (Memory Map), listed later in the data sheet, lists all programmable control signals and their addresses.

Real time control is accomplished via the EN and DATA\_# pins. Real time observation is accomplished via the per-pin or central monitor.

# **Applications**

- · Automated Test Equipment

- Logic/ASIC Verifiers

- Instrumentation

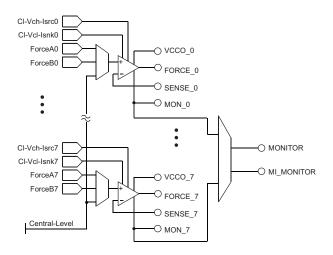

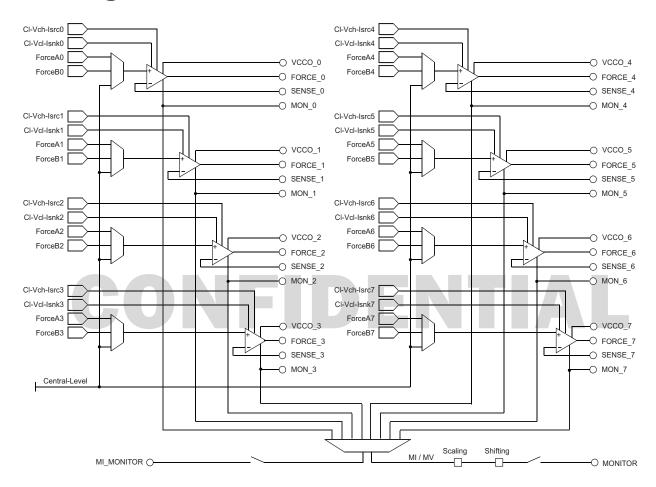

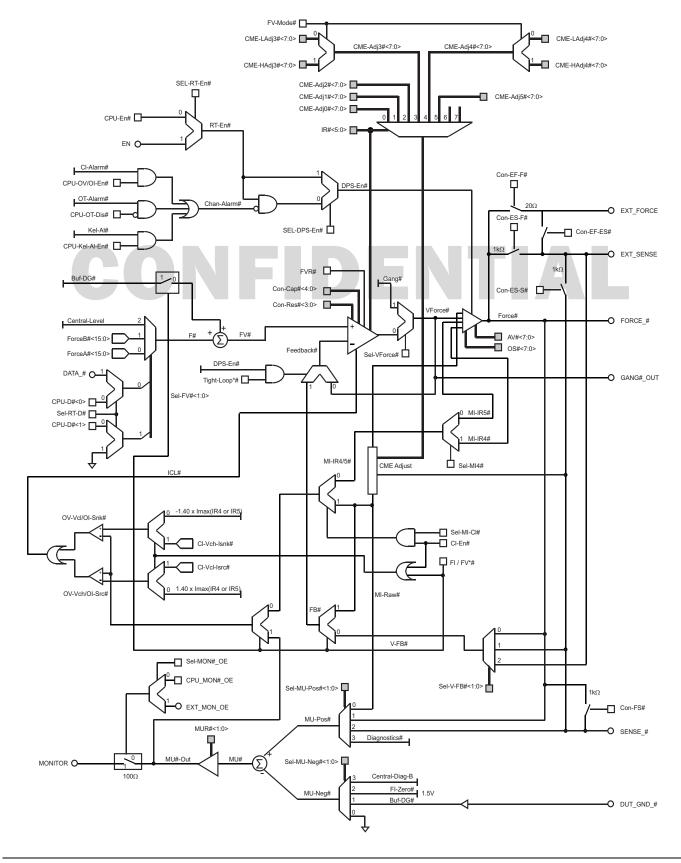

# **Block Diagram**

## **Features**

- Per Channel DPS

- FV, FI, MV, MI, HiZ Capability

- 16V Measure Voltage Input Compliance Range

- 2 Force Voltage Ranges (8V, 16V)

- 3 Measure Voltage Ranges (4V, 8V, 16V)

- 6 Current Ranges: (512mA, 25.6mA, 2.56mA, 256μA, 25.6μA, 2.56μA)

- Programmable Voltage and Current Clamps

- · Power Management

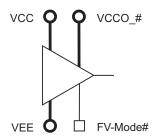

- Independent Output Buffer Power Supply (VCCO)

- Ability to Exceed VCCO in Lower Current Ranges (Patent Pending)

- · Flexible Ganging Capability

- No Restrictions on Maximum # DPS Units

- Protection

- On-Chip Junction Temperature Monitor

- Over-Temperature Shut Down per Chip

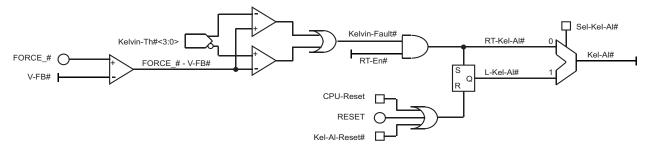

- Kelvin Connection Sensing/Alarm per Channel

- Over-Current Sensing/Alarm per Channel

- Global External Force/Sense Connectable to any Channel

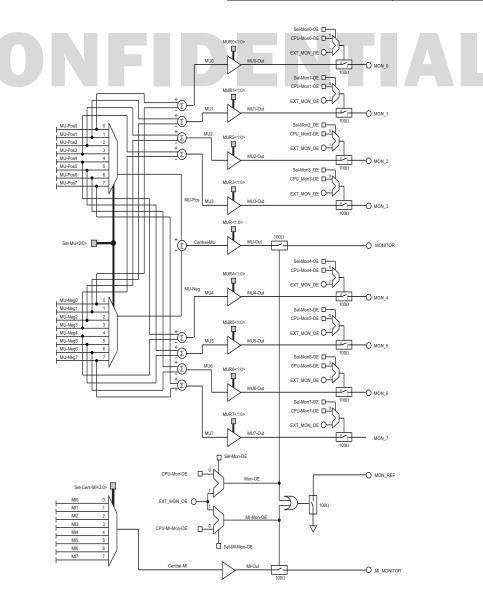

- Monitor

- Per-pin Monitor for enhanced throughput

- HiZ Capability

- Scaling and Shifting Capability

- One General Purpose Central Monitor per Chip

- Scaling and Shifting Capability

- HiZ Capability

- One Dedicated Measure Current Monitor per Chip

- HiZ Capability

- 3-Bit Serial CPU Port

- On-Chip DAC to Generate DC Levels

- 2 Independent FV Levels/Channel

- Central Resource Mode w/16 Selectable Levels

- Independent Source and Sink Clamp Levels/Channel

- 16 bits/Level

- On-Chip Offset and Gain Correction per Level

- · Package/Power Dissipation

- Pb-Free (RoHS Compliant)

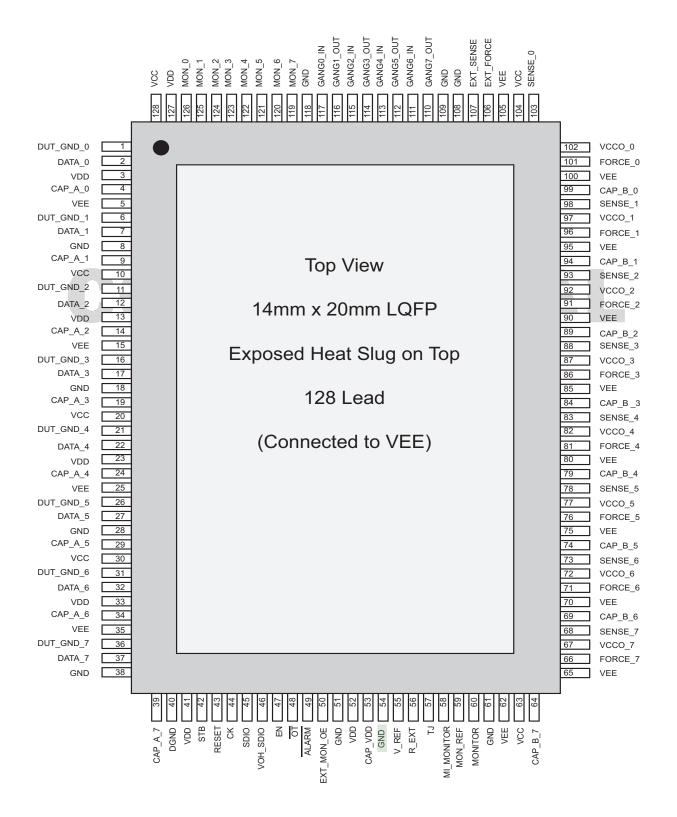

- 128 Lead, 14mmx20mm, LQFP w/Exp Heat Slug

- Pdg 115mW/Channel; Pdg 920mW/Chip

# **Block Diagram**

# **Table of Contents**

| Pin Descriptions                                                 | . 6 |

|------------------------------------------------------------------|-----|

| Pin Configuration                                                | . 8 |

| Absolute Maximum Ratings                                         | . 9 |

| Recommended Operating Conditions                                 | 10  |

| DC Characteristics                                               |     |

| DC Electrical Specifications – Power Supply Current              |     |

| DC Electrical Specifications – Thermal Monitor and Alarm         |     |

| DC Electrical Specifications – CPU Port                          |     |

| DC Electrical Specifications – Digital Impuls                    |     |

| DC Electrical Specifications – Analog Pins                       |     |

| DC Electrical Specifications – DAC Calibration                   |     |

| DC Electrical Specifications - DAC                               |     |

| DC Electrical Specifications - Force Voltage                     |     |

| DC Electrical Specifications - Measure Current                   | 16  |

| DC Electrical Specifications – Force Current                     |     |

| DC Electrical Specifications – Current Clamps                    |     |

| DC Electrical Specifications – Measure Voltage - Central Monitor |     |

| DC Electrical Specifications – Switch Resistance Values          |     |

| DC Electrical Specifications - Kelvin Alarms                     |     |

| DC Electrical Specifications – Central Level Gain and Offset     | 24  |

| AC Characteristics                                               |     |

| AC Electrical Specifications – CPU Port                          |     |

| AC Electrical Specifications - DPS                               |     |

| Chip Overview                                                    |     |

| CPU Control                                                      |     |

| Real Time Control                                                |     |

| External Signal Nomenclature                                     |     |

| CPU Programmed Control Line Nomenclature                         |     |

| Block Diagrams                                                   |     |

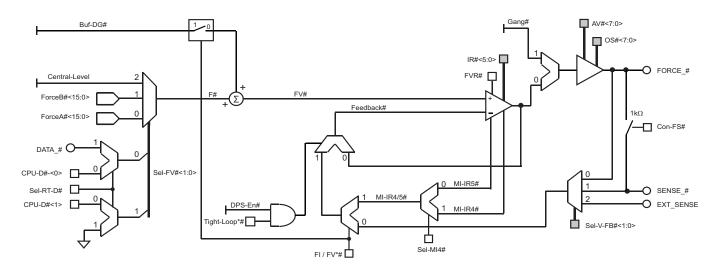

| Per Channel Diagram                                              |     |

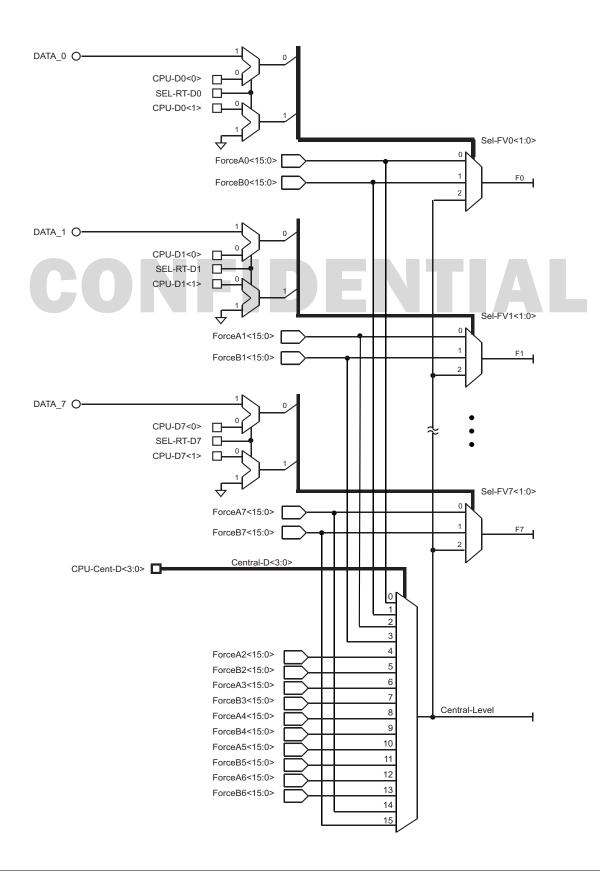

| Central Resource vs. Channel Mode                                |     |

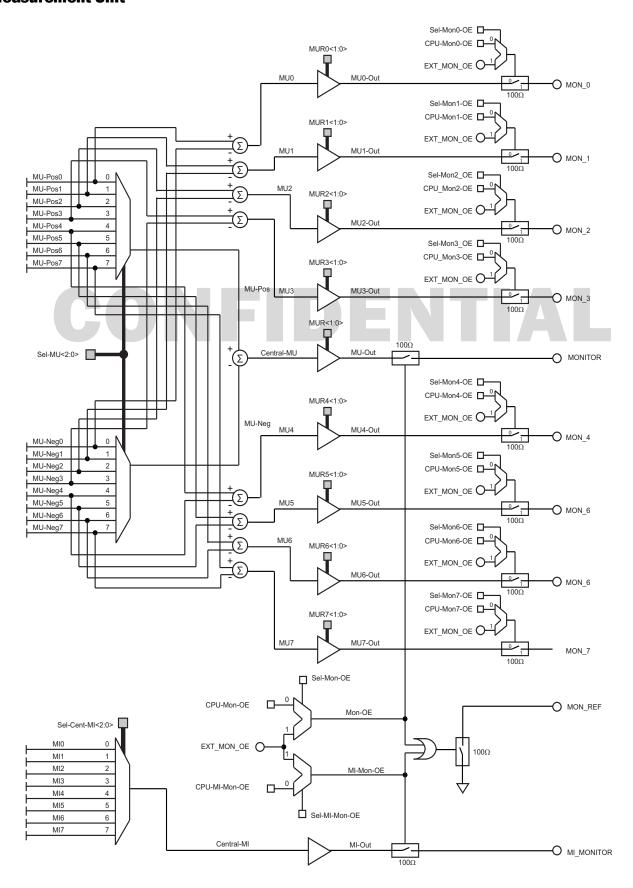

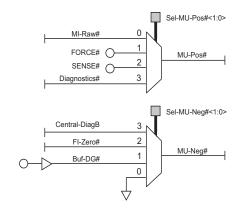

| Measurement Unit                                                 |     |

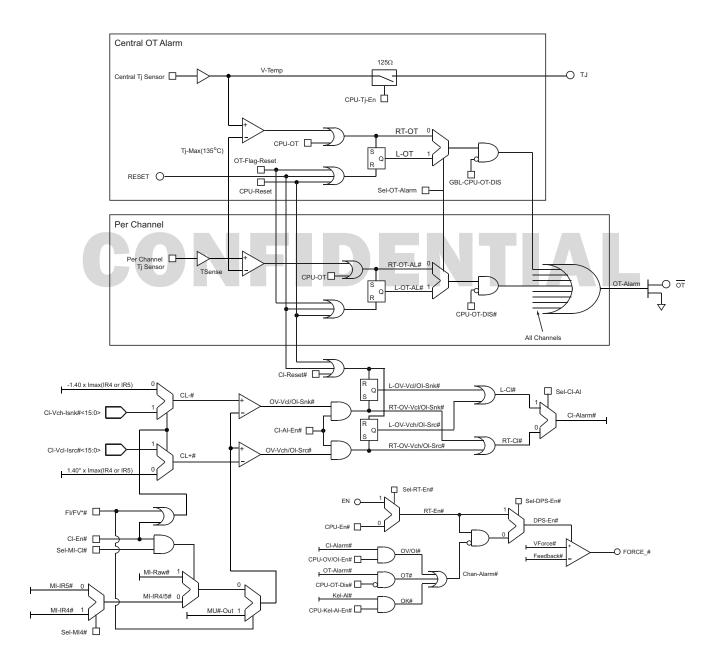

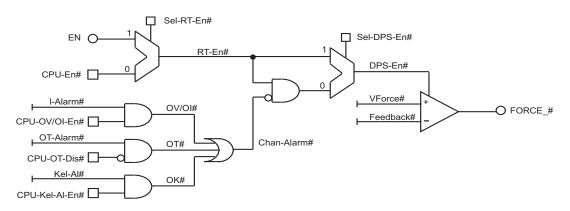

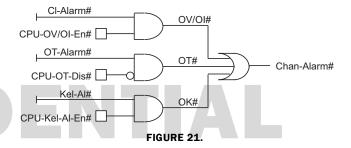

| OI, OT and Kelvin Alarm                                          |     |

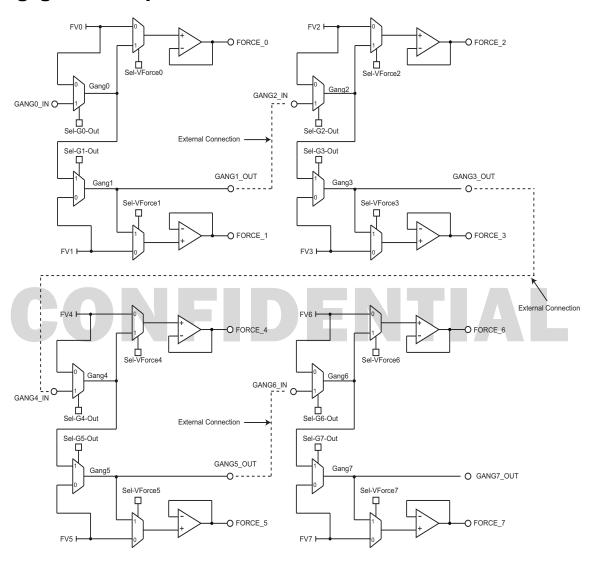

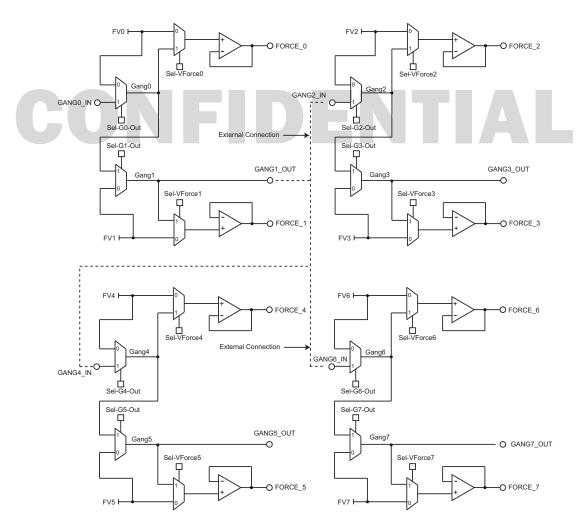

| Serial Ganging with One Chip                                     |     |

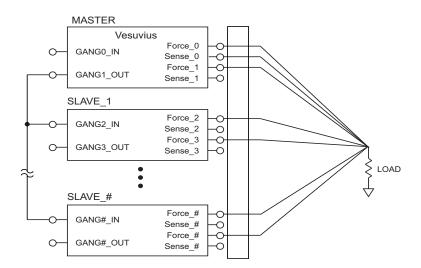

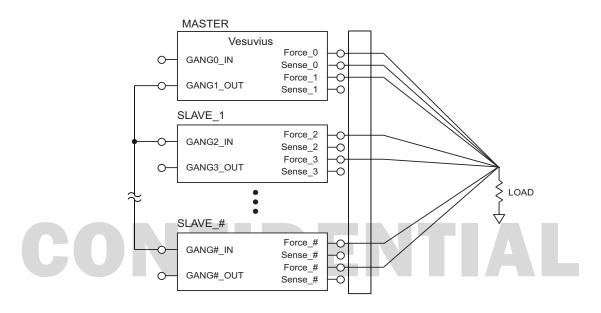

| Ganging Across Multiple Vesuvius Devices                         |     |

| Overview                                                         |     |

| Mode Selection                                                   |     |

| Current Ranges High Impedance                                    |     |

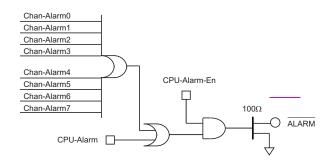

| Channel Alarm                                                    |     |

| Force Voltage                                                    |     |

| Forcing Op Amp Input Source                                      |     |

| Per Channel Mode                                                 |     |

| Central Resource Mode                                            |     |

| External Resource Mode                                           | 34  |

| Central Level Calibration                                       |    |

|-----------------------------------------------------------------|----|

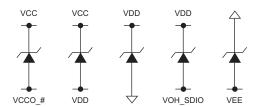

| VCCO_#                                                          |    |

| Voltage and Current Clamps                                      |    |

| Short Circuit Limit                                             |    |

| Programmable Current Clamps                                     |    |

| Clamp Source                                                    |    |

| Force Current                                                   |    |

| Ganging                                                         | 40 |

| Serial Chip-to-Chip Ganging                                     | 41 |

| Measurement Unit  Measurement Unit Input Sources                | 41 |

| Measure Voltage                                                 |    |

| Measure Current                                                 |    |

| Changing Current Ranges                                         |    |

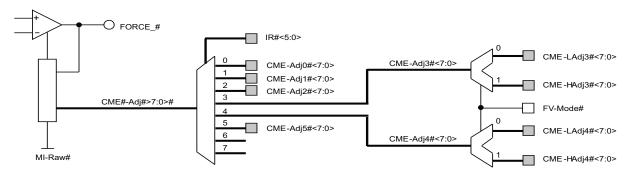

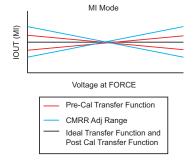

| CME (Common Mode Error) Calibration                             | 43 |

| IR3 and IR4                                                     |    |

| Monitor Output Current Limiting                                 |    |

| Monitor High Impedance                                          |    |

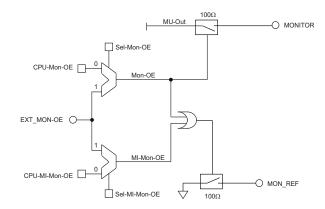

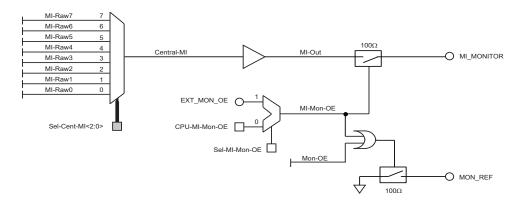

| Measurement Current Monitor                                     |    |

| MI Monitor High Impedance                                       |    |

| MI Monitor Reference                                            |    |

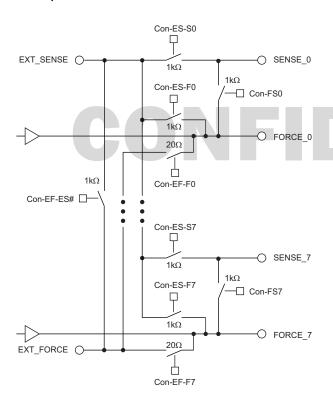

| External Force and Sense                                        | 46 |

| EXT_FORCE                                                       |    |

| EXT_SENSE                                                       |    |

| Force/Sense Connect Switch                                      |    |

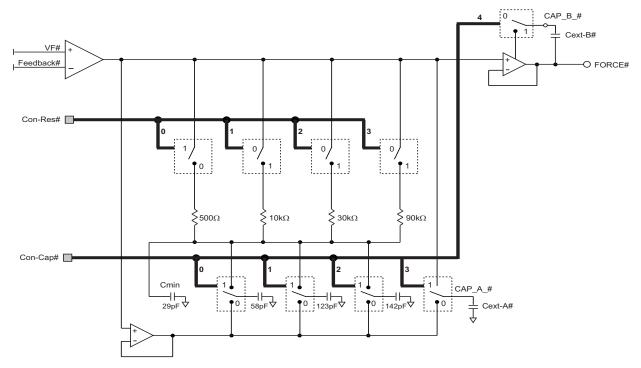

| Programmable Compensation Network                               |    |

| Calculation of Zeros based on Internal Capacitors and Resistors |    |

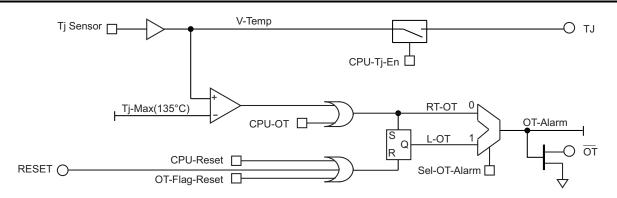

| Over-temperature Protection                                     |    |

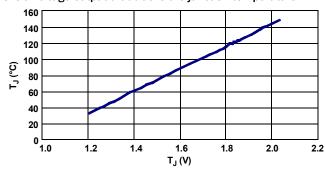

| Temperature Monitor                                             | 49 |

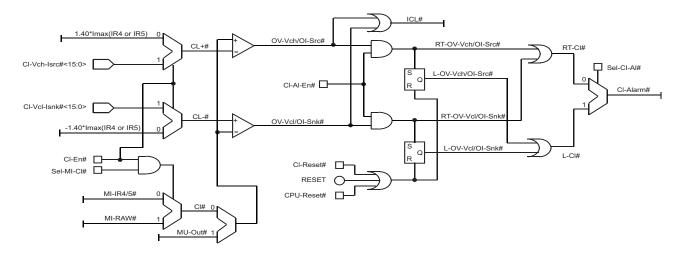

| Clamp Alarm                                                     |    |

| Clamp Alarm Readback                                            |    |

| Current Clamps vs Current Alarms                                |    |

| Chip Alarm                                                      |    |

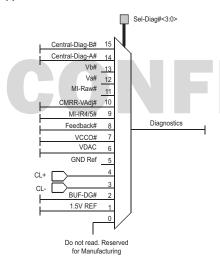

| Diagnostics                                                     |    |

| Temperature Sensing                                             |    |

| Required Off-Chip Components                                    |    |

| _                                                               |    |

| Device Under Test Ground                                        |    |

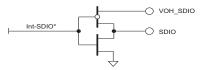

| VOH_SDIO                                                        |    |

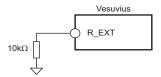

| R_EXT                                                           |    |

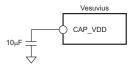

| CAP_VDD                                                         | 53 |

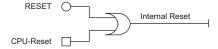

| Chip ResetChip Reset                                            | 53 |

| Power Supply Restrictions                               |    |

|---------------------------------------------------------|----|

| Power Supply/Analog Voltage Sequence                    |    |

| DC Levels                                               |    |

| Voltage Level Programming                               |    |

| Level Programming                                       |    |

| Current Clamp Programming                               |    |

| DC Calibration and Level Test Procedure                 |    |

| DAC Calibration.                                        |    |

| CPU Port                                                |    |

| Address                                                 |    |

| Data                                                    |    |

| Control Signals                                         |    |

| Clock Requirements.                                     |    |

| Write Enable                                            |    |

| Read vs Write Cycle                                     | 57 |

| "Any Channel" Write                                     |    |

| Channel Read Back                                       |    |

| Chip ID                                                 |    |

| Address Space                                           | 58 |

| Address Description                                     |    |

| DAC Sample and Hold (S/H) State Machine                 |    |

| Protocol Timing Diagram                                 |    |

| Per Pin Registers                                       |    |

| Central Resource Registers                              |    |

| Thermal Analysis                                        |    |

| Junction Temperature                                    |    |

| Conduction                                              |    |

| Convection                                              |    |

| θJC Calculation                                         |    |

| Intrinsic Thermal Conductivity                          |    |

| •                                                       |    |

| Manufacturing Information                               |    |

| PCB Assembly                                            |    |

| Solder Profile.                                         |    |

|                                                         |    |

| Recommended PCB Footprint                               |    |

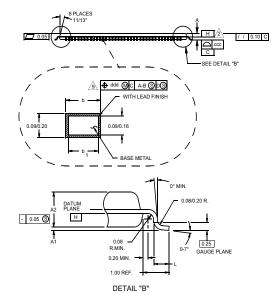

| Package Outline Drawing                                 | 68 |

| Revision History                                        | 69 |

| Ordering Information                                    | 71 |

| Appendix                                                |    |

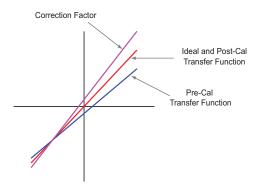

| 1. Calibration Overview                                 | 72 |

| 2. Calibration Basics                                   |    |

| 3. DC Calibration.                                      |    |

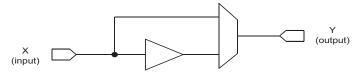

| 4. Vesuvius DPS Channel Overview                        |    |

| 5. Hardware/Software Calibration Distinction            | 74 |

| 6. Total Chip Calibration Procedure Outline             |    |

| 7. DC Level Output Equation for Force Voltage DAC Level |    |

| 8. DC Level Memory RAM Code Calculation                 |    |

| 9. Basic Force Voltage Setup                            |    |

| 10.Total Chip Calibration Detailed Procedure            | 78 |

# **Pin Descriptions**

| PIN#        | PIN NAME                    | DESCRIPTION                                            |

|-------------|-----------------------------|--------------------------------------------------------|

| 101, 103, 1 | FORCE_0, SENSE_0, DUT_GND_0 | Channel 0 force, sense, and DUT ground pins.           |

| 2           | DATA_0                      | Channel 0 data input pin.                              |

| 102         | vcco_o                      | Positive analog supply for the Channel 0 output stage. |

| 4, 99       | CAP_A_0, CAP_B_0            | Channel 0 op amp compensation capacitor pins.          |

| 126         | MON_O                       | Channel 0 V/I monitor output pin.                      |

| 96, 98, 6   | FORCE_1, SENSE_1, DUT_GND_1 | Channel 1 force, sense, and DUT ground pins.           |

| 7           | DATA_1                      | Channel 1 data input pin.                              |

| 97          | VCCO_1                      | Positive analog supply for the Channel 1 output stage. |

| 9, 94       | CAP_A_1, CAP_B_1            | Channel 1 op amp compensation capacitor pins.          |

| 125         | MON_1                       | Channel 1 V/I monitor output pin.                      |

| 91, 93, 11  | FORCE_2, SENSE_2, DUT_GND_2 | Channel 2 force, sense, and DUT ground pins.           |

| 12          | DATA_2                      | Channel 2 data input pin.                              |

| 92          | VCCO_2                      | Positive analog supply for the Channel 2 output stage. |

| 14, 89      | CAP_A_2, CAP_B_2            | Channel 2 op amp compensation capacitor pins.          |

| 124         | MON_2                       | Channel 2 V/I monitor output pin.                      |

| 86, 88, 16  | FORCE_3, SENSE_3, DUT_GND_3 | Channel 3 force, sense, and DUT ground pins.           |

| 17          | DATA_3                      | Channel 3 data input pin.                              |

| 87          | vcco_3                      | Positive analog supply for the Channel 3 output stage. |

| 19, 84      | CAP_A_3, CAP_B_3            | Channel 3 op amp compensation capacitor pins.          |

| 123         | MON_3                       | Channel 3 V/I monitor output pin.                      |

| 81, 83, 21  | FORCE_4, SENSE_4, DUT_GND_4 | Channel 4 force, sense, and DUT ground pins.           |

| 22          | DATA_4                      | Channel 4 data input pin.                              |

| 82          | VCCO_4                      | Positive analog supply for the Channel 4 output stage. |

| 24, 79      | CAP_A_4, CAP_B_4            | Channel 4 op amp compensation capacitor pins.          |

| 122         | MON_4                       | Channel 4 V/I monitor output pin.                      |

| 76, 78, 26  | FORCE_5, SENSE_5, DUT_GND_5 | Channel 5 force, sense, and DUT ground pins.           |

| 27          | DATA_5                      | Channel 5 data input pin.                              |

| 77          | VCCO_5                      | Positive analog supply for the Channel 5 output stage. |

| 29, 74      | CAP_A_5, CAP_B_5            | Channel 5 op amp compensation capacitor pins.          |

| 121         | MON_5                       | Channel 5 V/I monitor output pin.                      |

| 71, 73, 31  | FORCE_6, SENSE_6, DUT_GND_6 | Channel 6 force, sense, and DUT ground pins.           |

| 32          | DATA_6                      | Channel 6 data input pin.                              |

| 72          | vcco_6                      | Positive analog supply for the Channel 6 output stage. |

| 34, 69      | CAP_A_6, CAP_B_6            | Channel 6 op amp compensation capacitor pins.          |

| 120         | MON_6                       | Channel 6 V/I monitor output pin.                      |

| 66, 68, 36  | FORCE_7, SENSE_7, DUT_GND_7 | Channel 7 force, sense, and DUT ground pins.           |

| 37          | DATA_7                      | Channel 7 data input pin.                              |

| 67          | VCCO_7                      | Positive analog supply for the Channel 7 output stage. |

| 39, 64      | CAP_A_7, CAP_B_7            | Channel 7 op amp compensation capacitor pins.          |

| PIN#                                                       | PIN NAME                                                    | DESCRIPTION                                                      |

|------------------------------------------------------------|-------------------------------------------------------------|------------------------------------------------------------------|

| 119                                                        | MON_7                                                       | Channel 7 V/I monitor output pin.                                |

| 55, 56                                                     | V_REF, R_EXT                                                | External precision voltage and resistance reference.             |

| 57, 48, 49                                                 | TJ, ŌT, ĀLĀRM                                               | On-chip die temperature monitor, OT flag and alarm outputs.      |

| 47                                                         | EN                                                          | Real time HiZ control pin.                                       |

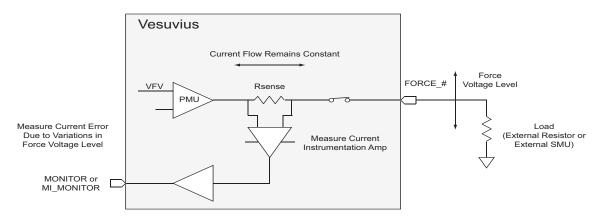

| 60, 58                                                     | MONITOR, MI_MONITOR                                         | Central monitor and measure current monitor analog outputs.      |

| 59, 50                                                     | MON_REF, EXT_MON_OE                                         | Monitor negative reference output and external HiZ control pins. |

| 44, 45, 42, 43                                             | CK, SDIO, STB, RESET                                        | Serial port control pins.                                        |

| 106, 107                                                   | EXT_FORCE, EXT_SENSE Central external force and sense pins. |                                                                  |

| 117, 116                                                   | GANGO_IN, GANG1_OUT                                         | External ganging pins for Channels 0 and 1.                      |

| 115, 114                                                   | GANG2_IN, GANG3_OUT                                         | External ganging pins for Channels 2 and 3.                      |

| 113, 112                                                   | GANG4_IN, GANG5_OUT                                         | External ganging pins for Channels 4 and 5.                      |

| 111, 110                                                   | GANG6_IN, GANG7_OUT                                         | External ganging pins for Channels 6 and 7.                      |

| 10, 20, 30, 63, 104, 128                                   | VCC                                                         | Analog positive power supply.                                    |

| 5, 15, 25, 35, 62, 65, 70, 75,<br>80, 85, 90, 95, 100, 105 | VEE                                                         | Analog negative voltage supply                                   |

| 3, 13, 23, 33, 41, 52, 127                                 | VDD                                                         | Digital power supply.                                            |

| 8, 18, 28, 38, 51, 54, 61,<br>108, 109, 118                | GND                                                         | Chip ground.                                                     |

| 40                                                         | DGND                                                        | Digital ground.                                                  |

| 46                                                         | VOH_SDIO                                                    | Positive supply rail to the SDIO output pin.                     |

| 53                                                         | CAP_VDD                                                     | External filter capacitor for VDD.                               |

# **Pin Configuration**

# **Absolute Maximum Ratings**

| Parameter                    | Min        | Тур | Max       | Units |

|------------------------------|------------|-----|-----------|-------|

| Power Supplies               |            |     |           | 1     |

| vcc                          | VDD - 0.5  |     | +15       | V     |

| vcco_#                       | -0.5       |     | VCC + 0.5 | V     |

| VEE                          | -5         |     | 0.5       | V     |

| VDD                          | -0.5       |     | +5        | V     |

| VCC - VEE                    | -0.5       |     | 17.5      | V     |

| VDD - VEE                    |            | +8  |           | V     |

| Digital Pins                 |            |     |           | 1     |

| CK, SDIO, STB, RESET         | GND - 0.5V |     | VDD + 0.5 | V     |

| SENSE                        | GND - 0.5V |     | VDD + 0.5 | V     |

| MONITOR                      | GND - 0.5V |     | VDD + 0.5 | V     |

| ALARM, OT                    | GND - 0.5V |     | VDD + 0.5 | V     |

| CENTRAL_D_#                  | GND - 0.5V |     | VDD + 0.5 | v     |

| EN                           | GND - 0.5V |     | VDD + 0.5 | V     |

| DATA_#                       | GND - 0.5V |     | VDD + 0.5 | V     |

| SDIO Output Current          | -20        |     | +20       | mA    |

| External References          |            |     |           |       |

| R_EXT                        |            | 10  |           | ΚΩ    |

| V_REF                        | GND - 0.5V |     | VDD + 0.5 | V     |

| Analog Pins                  |            |     |           |       |

| FORCE_#                      | VEE - 0.5  |     | VCC + 0.5 | V     |

| SENSE_#                      | VEE - 0.5  |     | VCC + 0.5 | V     |

| MONITOR                      | GND - 0.5  | 20  | VDD + 0.5 | V     |

| MI_MONITOR                   | GND - 0.5  | 20  | VDD + 0.5 | V     |

| EXT_SENSE                    | VEE - 0.5  |     | VCC + 0.5 | V     |

| EXT_FORCE                    | VEE - 0.5  |     | VCC + 0.5 | V     |

| GANG#_IN                     | VEE - 0.5  |     | VCC + 0.5 | V     |

| GANG#_OUT                    | VEE - 0.5  |     | VCC + 0.5 | V     |

| TEST+, TEST-                 | GND - 0.5  | 20  | VDD + 0.5 | V     |

| UT                           | GND - 0.5  | 20  | VDD + 0.5 | V     |

| DUT_GND                      | VEE - 0.5  |     | VCC + 0.5 | V     |

| Thermal Information          |            |     |           | •     |

| Maximum Junction Temperature |            |     | 150       | °C    |

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

# **Recommended Operating Conditions**

| Parameter                                       | Min          | Тур                        | Max                | Units |  |  |  |

|-------------------------------------------------|--------------|----------------------------|--------------------|-------|--|--|--|

| Power Supplies                                  |              | <u> </u>                   | I                  | ı     |  |  |  |

| vcc                                             | +8           |                            | +14                | V     |  |  |  |

| vcco_#                                          | FORCE_# +0.5 |                            | VCC                | v     |  |  |  |

| VEE                                             | -4           |                            | -2                 | V     |  |  |  |

| VDD                                             | +3.25        |                            | 3.45               | V     |  |  |  |

| VCC - VEE                                       | +10          |                            | +16                | V     |  |  |  |

| VCCO_# - VEE                                    | +6           |                            | +16                | v     |  |  |  |

| VDD - VEE                                       | +.525        |                            | +7.4               | V     |  |  |  |

| Digital Pins                                    |              |                            |                    |       |  |  |  |

| CK, SDIO, STB, RESET                            | GND          |                            | VDD                | V     |  |  |  |

| EXT_MON_OE                                      | GND          |                            | VDD                | V     |  |  |  |

| EN                                              | GND          |                            | VDD                | V     |  |  |  |

| DATA_#                                          | GND          |                            | VDD                | V     |  |  |  |

| CENTRAL_D_#                                     | GND          |                            | VDD                | V     |  |  |  |

| ALARM, OT                                       | GND          |                            | VDD                | V     |  |  |  |

| External References                             |              |                            |                    |       |  |  |  |

| V_REF                                           | +2.99        |                            | 3.01               | v     |  |  |  |

| R_EXT                                           | 10           | 0KΩ ± 0.1% tempco = 25 $ $ | .1% tempco = 25ppm |       |  |  |  |

| Analog Pins                                     |              |                            |                    |       |  |  |  |

| FORCE_# (HiZ Compliance)                        | VEE          |                            | vcc                | V     |  |  |  |

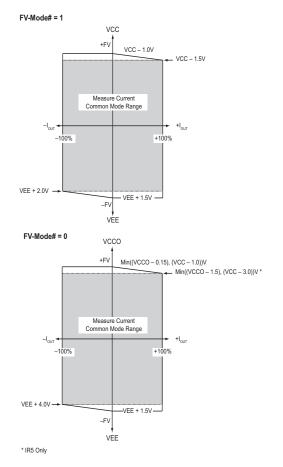

| IRO - IR5 (FV Mode# = 0)                        |              |                            |                    |       |  |  |  |

| FORCE_# (Active, FV, I <sub>OUT</sub> = 0)      | VEE + 1.5 to | o Min of ((VCCO - 0.15) o  | r (VCC - 1.0))     | v     |  |  |  |

| FORCE_# (Active, FV, ±I <sub>MAX,</sub> ±512mA) | VEE + 4.0 t  | o Min of ((VCCO - 1.5) or  | ((VCC - 3.0))      | V     |  |  |  |

| IRO - IR4 (FV Mode# = 1)                        |              |                            |                    |       |  |  |  |

| FORCE_# (Active, FV, I <sub>OUT</sub> = 0)      | VEE + 1.5    |                            | VCC - 1.0          | v     |  |  |  |

| FORCE_# (Active, FV, ±I <sub>MAX</sub> )        | VEE + 2.0    |                            | VCC - 1.5          | V     |  |  |  |

| IR5 (FV Mode# = 1)                              |              |                            |                    |       |  |  |  |

| FORCE_# (Active, FV, ±I <sub>MAX</sub> )        | N/A          |                            | N/A                | N/A   |  |  |  |

| SENSE_#                                         | VEE          |                            | VCC                | V     |  |  |  |

| MONITOR                                         | GND          |                            | VDD                | V     |  |  |  |

| MI_MONITOR                                      | GND          |                            | VDD                | V     |  |  |  |

| EXT_SENSE                                       | VEE          |                            | VCC                | V     |  |  |  |

| EXT_FORCE                                       | VEE          |                            | vcc                | V     |  |  |  |

| GANG#_IN, GANG#_OUT                             | VEE + 1.5    |                            | VCC - 1.5          | V     |  |  |  |

| TEST+, TEST-                                    | GND          |                            | VDD                | V     |  |  |  |

| ТЈ                                              | GND          |                            | VDD                | V     |  |  |  |

| Miscellaneous                                   |              |                            |                    |       |  |  |  |

| Junction Temperature                            | +25          |                            | 100                | °C    |  |  |  |

| CPU Port CK Frequency                           | 10           |                            | 25                 | MHz   |  |  |  |

| Capacitive Load at DOUT_# (IRO - IR5)           | 0            |                            | 50                 | μF    |  |  |  |

## **DC Characteristics**

For all of the following DC Electrical Specifications, compliance to datasheet limits is assured by one or more methods: production test, characterization and/or design.

## **DC Electrical Specifications - Power Supply Current**

VOH\_SDIO = VDD, V\_REF = +3V, DUT\_GND = 0V. Parameters with MIN and/or MAX limits are 100% tested at TA = +25 °C, unless otherwise specified. Temperature limits established by characterization and are not production tested.

| Spec #                    | PARAMETER   | TEST CONDITIONS                                                                                                                                          | MIN  | TYP   | MAX | UNITS | Pd (TYP)<br>mW/Chip |

|---------------------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|-----|-------|---------------------|

| NO LOAD, FV               | /-Mode# = 0 |                                                                                                                                                          |      |       |     |       | 1                   |

| 11100                     | ICC         |                                                                                                                                                          |      | 100   | 150 | mA    | 1250                |

| 11200                     | ICC_O       |                                                                                                                                                          |      | 1.3   | 35  | mA    | 5.5                 |

| 11300                     | IEE         | VCC = +12.5V, VCCO_# = +4.25V, VEE = -3.5V, VDD =<br>+3.45V, FV-Mode = 0, IR5, FV = +3V, Bbias = 1                                                       | -160 | -108  |     | mA    | 378                 |

| 11400                     | IDD         | 13.45V, 1V Mode 0, 110, 1V 13V, Bald3 1                                                                                                                  |      | 55    | 85  | mA    | 190                 |

| 11500                     | IOH_SDIO    |                                                                                                                                                          | -2.5 | 0     | 2.5 | mA    | 0                   |

| NO LOAD, FV               | /-Mode = 1  |                                                                                                                                                          |      |       |     |       |                     |

| 11110                     | ICC         |                                                                                                                                                          |      | 100   | 150 | mA    | 1250                |

| 11210                     | ICC_O       |                                                                                                                                                          |      | 0.5   | 3.5 | mA    | 2125                |

| 11310                     | IEE         | VCC = +12.5V, VCCO_# = +4.25V, VEE = -3.5V, VDD =<br>+3.45V, FV-Mode = 1, IR4, FV = +3V, Bbias = 0.                                                      | -160 | -108  |     | mA    | 378                 |

| 11410                     | IDD         | 10.40V,1V Mode 1, M4,1V 10V, Bbid5 0.                                                                                                                    |      | 55    | 85  | mA    | 190                 |

| 11510                     | IOH_SDIO    |                                                                                                                                                          | -25  | 0     | 2.5 | mA    | 0                   |

| +I <sub>MAX</sub> , FV-Mo | ode = 0     |                                                                                                                                                          |      |       |     |       | L                   |

| 11120                     | ICC         |                                                                                                                                                          |      | 188   | 195 | mA    | 2086                |

| 11220                     | ICC_O       | VCC = +12.5V, VCCO_# = +4.25V, VEE = -3.5V, VDD = +3.45V, +I <sub>MAX</sub> , IR5, FV-Mode = 0, FV = +3V, all 8 channels sourcing 512mA each, Bbias = 0. |      | 4.25  | 4.5 | Α     | 6039                |

| 11320                     | IEE         |                                                                                                                                                          | -365 | -350  |     | mA    | 1225                |

| 11420                     | IDD         |                                                                                                                                                          |      | 55    | 85  | mA    | 190                 |

| 11520                     | IOH_SDIO    |                                                                                                                                                          | -2.5 | 0     | 2.5 | mA    | 0                   |

| +I <sub>MAX</sub> , FV-Mo | ode = 1     |                                                                                                                                                          |      |       |     |       |                     |

| 11130                     | ICC         |                                                                                                                                                          |      | 325   | 365 | mA    | 2424                |

| 11230                     | ICC_O       | VCC = +12.5V, VCCO_# = +4.25V, VEE = -3.5V VDD = +3.45V,                                                                                                 |      | 0.5   | 30  | mA    | 2.1                 |

| 11330                     | IEE         | +I <sub>MAX</sub> , IR4, FV-Mode = 1, FV = +8V, all 8 channels sourcing                                                                                  | -160 | -123  |     | mA    | 430.5               |

| 11430                     | IDD         | 25.6mA each, Bbias = 0.                                                                                                                                  |      | 55    | 85  | mA    | 190                 |

| 11530                     | IOH_SDIO    |                                                                                                                                                          | -2.5 | 0     | 2.5 | mA    | 0                   |

| -I <sub>MAX</sub> , FV-Mo | ode = 0     |                                                                                                                                                          | •    |       |     | '     |                     |

| 11121                     | ICC         |                                                                                                                                                          |      | 341   | 350 | mA    | 4263                |

| 11221                     | ICC_O       | VCC = +12.5V, VCCO # = +4.25V, VEE = -3.5V, VDD =                                                                                                        |      | 30    | 40  | mA    | 128                 |

| 11321                     | IEE         | +3.45V, -I <sub>MAX</sub> , IR5, FV-Mode = 0, FV = +3V, all 8 channels                                                                                   | -4.5 | -4.47 |     | Α     | 27933               |

| 11421                     | IDD         | sinking 512mA each, Bbias = 1.                                                                                                                           |      | 55    | 85  | mA    | 190                 |

| 11521                     | IOH_SDIO    |                                                                                                                                                          | -2.5 | 0     | 2.5 | mA    | 0                   |

| -I <sub>MAX</sub> , FV-Mo | ode = 1     |                                                                                                                                                          |      |       |     |       |                     |

| 11131                     | ICC         |                                                                                                                                                          |      | 118   | 150 | mA    | 1475                |

| 11231                     | ICC_O       | VCC = +12.5V, VCCO_# = +4.25V, VEE = -3.5V VDD = +3.45V,                                                                                                 |      | 0.5   | 30  | mA    | 2.1                 |

| 11331                     | IEE         | -I <sub>MAX</sub> , IR4, FV-Mode = 1, FV = +8V, all 8 channels sinking                                                                                   | -365 | -325  |     | mA    | 2828                |

| 11431                     | IDD         | 25.6mA each, Bbias = 1.                                                                                                                                  |      | 55    | 85  | mA    | 190                 |

| 11531                     | IOH_SDIO    |                                                                                                                                                          | -2.5 | 0     | 2.5 | mA    | 0                   |

NOTE: The total chip power values are based upon typical supply currents and power supply levels indicated in the test conditions. For proper sizing of power supplies in the application, power to the DUT or load being driven the Vesuvius must also be accounted for.

#### **DC Electrical Specifications – Thermal Monitor and Alarm**

VOH\_SDIO = VDD, V\_REF = +3V, DUT\_GND = 0V. Parameters with MIN and/or MAX limits are 100% tested at TA = +25°C, unless otherwise specified. Temperature limits established by characterization and are not production tested.

| Spec # | PARAMETER                  | TEST CONDITIONS                                                                | MIN  | TYP      | MAX  | UNITS |

|--------|----------------------------|--------------------------------------------------------------------------------|------|----------|------|-------|

| TJ, OT |                            |                                                                                |      |          |      |       |

| 10996  | TJ HiZ Leakage             | VCC = +12.5V, VCCO_# = +4.25V, VEE = -3.5V, VDD = +3.45V, Tested at 0V and VDD | -500 | 0        | +500 | nA    |

|        | Over-Temperature Threshold | VCC = +13V, VCCO_# = +4V, VEE = -3V, VDD = +3.3V                               |      | 135 ± 15 | 150  | °C    |

| 10994  | OT VOH (HiZ Leakage)       | VCC = +12.5V, VCCO_# = +4.25V, VEE = -3.5V, VDD = +3.45V, Tested at OV and VDD | -100 | 0        | +100 | nA    |

|        | OT VOL                     | VOH_SDIO = VDD, V_REF = +3V, DUT_GND = 0V, Input current = 2mA                 |      |          | 0.4  | ٧     |

#### **DC Electrical Specifications - CPU Port**

VOH\_SDIO = VDD, V\_REF = +3V, DUT\_GND = 0V. Parameters with MIN and/or MAX limits are 100% tested at TA = +25 °C, unless otherwise specified. Temperature limits established by characterization and are not production tested.

| Spec #    | PARAMETER                               | TEST CONDITIONS                                                                                                          | MIN | TYP | MAX | UNITS |

|-----------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|

| SDIO, CK, | STB, RESET                              | NEIDENI                                                                                                                  |     |     |     |       |

| 17100     | VIH                                     | VCC = +12.5V, VCCO_# = +4.25V, VEE = -3.5V, VDD = +3.3V                                                                  | 1.6 |     |     | V     |

| 17110     | VIL                                     | VCC = +12.5V, VCCO_# = +4.25V, VEE = -3.5V, VDD = +3.3V                                                                  |     |     | 0.8 | V     |

| 17120     | I <sub>IN</sub> (Input Leakage Current) | VCC = +12.5V, VCCO_# = +4.25V, VEE = -3.5V, VDD = +3.45V, VOH_SDIO = VDD, V_REF = +3V, DUT_GND = 0, tested at OV and VDD | -1  | 0   | +1  | μΑ    |

| 17200     | VOH (SDIO Only)                         | VCC = +12.5V, VCCO_# = +4.25V, VEE = -3.5V, VDD = +3.3V, VOH_SDIO = VDD, I <sub>LOAD</sub> = 8mA                         | 2.4 |     |     | V     |

| 17210     | VOL (SDIO Only)                         | VCC = +12.5V, VCCO_# = +4.25V, VEE = -3.5V, VDD = +3.3V, VOH_SDIO = VDD, I <sub>LOAD</sub> = 8mA                         |     |     | 0.8 | V     |

#### **DC Electrical Specifications - Digital Inputs**

VOH\_SDIO = VDD, V\_REF = +3V, DUT\_GND = 0V. Parameters with MIN and/or MAX limits are 100% tested at TA = +25 °C, unless otherwise specified. Temperature limits established by characterization and are not production tested.

| Spec #     | PARAMETER                                        | TEST CONDITIONS                                                                | MIN | TYP | MAX | UNITS |

|------------|--------------------------------------------------|--------------------------------------------------------------------------------|-----|-----|-----|-------|

| EN, DATA_# |                                                  |                                                                                |     |     |     |       |

| 13260      | VIH                                              | VCC = +12.5V, VCCO_# = +4.25V, VEE = -3.5V, VDD = +3.3V                        | 2.0 |     |     | V     |

| 13261      | VIL                                              | VCC = +12.5V, VCCO_# = +4.25V, VEE = -3.5V, VDD = +3.3V                        |     |     | 0.8 | V     |

| 13262      | I <sub>IN</sub> (Input Leakage<br>Current) (HiZ) | VCC = +12.5V, VCCO_# = +4.25V, VEE = -3.5V, VDD = +3.45V, tested at OV and VDD | -1  | 0   | +1  | μΑ    |

#### **DC Electrical Specifications – Digital Outputs**

$VOH\_SDIO = VDD$ ,  $V\_REF = +3V$ ,  $DUT\_GND = 0V$ . Parameters with MIN and/or MAX limits are 100% tested at TA = +25 °C, unless otherwise specified. Temperature limits established by characterization and are not production tested.

| Spec # | PARAMETER         | TEST CONDITIONS                                                                | MIN  | TYP | MAX  | UNITS |

|--------|-------------------|--------------------------------------------------------------------------------|------|-----|------|-------|

| ALARM  |                   |                                                                                |      |     |      |       |

| 13360  | VOL (Sinking 4mA) | VCC = +12.5V, VCCO_# = +4.25V, VEE = -3.5V, VDD = +3.3V                        |      |     | 0.4  | V     |

| 13361  | VOH (HiZ Leakage) | VCC = +12.5V, VCCO_# = +4.25V, VEE = -3.5V, VDD = +3.45V, tested at OV and VDD | -100 |     | +100 | nA    |

## **DC Electrical Specifications - Analog Pins**

VCC = +12.5V,  $VCCO_{\#} = 4.25V$ , VEE = -3.5V, VDD = +3.45V,  $VOH_{SDIO} = VDD$ ,  $V_{REF} = +3V$ ,  $DUT_{GND} = 0V$ . Parameters with MIN and/or MAX limits are 100% tested at TA = +25 °C, unless otherwise specified. Temperature limits established by characterization and are not production tested.

| Spec #    | PARAMETER                           | TEST CONDITIONS                                                      | MIN  | TYP | MAX  | UNITS |  |

|-----------|-------------------------------------|----------------------------------------------------------------------|------|-----|------|-------|--|

| Leakage/I | eakage/Input Currents               |                                                                      |      |     |      |       |  |

| 10999     | V_REF Input Current                 |                                                                      | -1   |     | +1   | μΑ    |  |

| 10998     | DUT_GND Input Current               | Tested at -1V, OV and +1V                                            | -15  |     | +15  | nA    |  |

| 10700     | EXT_FORCE, EXT_SENSE in HiZ         | Tested at OV, VCC, VEE                                               | -15  |     | +15  | nA    |  |

| 10800     | GANG#_IN Input Current              | Tested at VCC - 1.5V, VEE + 1.5V                                     | -1   |     | +1   | μΑ    |  |

| 10801     | GANG#_OUT HiZ Leakage<br>Current    | Tested at VCC - 1.5V, VEE + 1.5V, Sel-G#-OUT and Sel-G(#-1)- OUT = 1 | -1   |     | +1   | μΑ    |  |

| 20210     | CAP_A_#, CAP_B_# Leakage<br>Current |                                                                      | -100 |     | +100 | nA    |  |

| 20560     | CAP_VDD Leakage Current             | Not production tested.                                               | -15  |     | +15  | μΑ    |  |

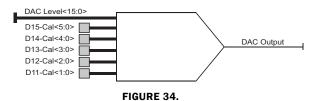

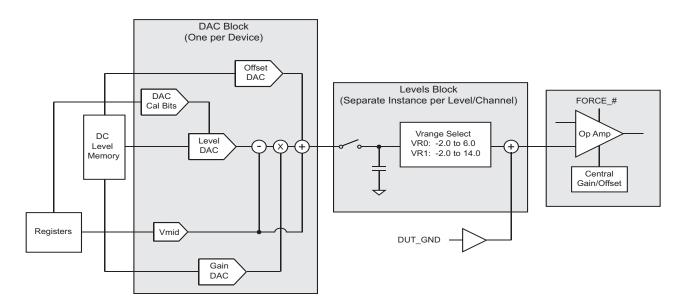

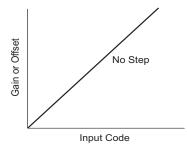

#### **Level DAC Calibration**

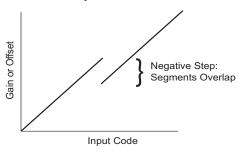

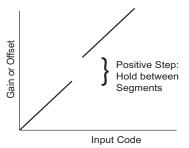

All DC tests are performed after the DAC is first calibrated. The upper 5 bits of the DAC are calibrated in the sequence D11 to D15. The DAC Cal bits are adjusted to make the major carry error as small as possible.

#### **DC Electrical Specifications - DAC Calibration**

VCC = +12V,  $VCCO_{\#} = +4V$ , VEE = -4V, VDD = +3.3V,  $DUT_{\_}GND = 0V$ . Parameters with MIN and/or MAX limits are 100% tested at TA = +25 °C, unless otherwise specified. Temperature limits established by characterization and are not production tested.

| SPEC# | PARAMETER                | TEST CONDITIONS                                                                             | MIN | TYP | MAX | UNITS |

|-------|--------------------------|---------------------------------------------------------------------------------------------|-----|-----|-----|-------|

| 16510 | Level DAC D15 Step Error | (DAC @ 8000 - DAC @ 7FFF)/(8000 - 7FFF) - DAC LSB; VR0, Code<br>8000 - Code 7FFF - LSB; VR0 | -2  |     | +2  | mV    |

| 16520 | Level DAC D14 Step Error | (DAC @ 7000 - DAC @ 3000)/(7000 - 3000) - DAC LSB; VR0,<br>Code 4000 - Code 3FFF - LSB; VR0 | -2  |     | +2  | mV    |

| 16530 | Level DAC D13 Step Error | (DAC @ 7000 - DAC @ 5000)/(7000 - 5000) - DAC LSB; VRO,<br>Code 6000 - Code 5FFF - LSB; VRO | -2  |     | +2  | mV    |

| 16540 | Level DAC D12 Step Error | (DAC @ 7000 - DAC @ 6000)/(7000 - 6000) - DAC LSB; VRO,<br>Code 7000 - Code 6FFF - LSB; VRO | -2  |     | +2  | mV    |

| 16550 | Level DAC D11 Step Error | (DAC @ 7800 - DAC @ 7000)/(7800 - 7000) - DAC LSB; VRO,<br>Code 7800 - Code 77FF - LSB; VRO | -2  |     | +2  | mV    |

| 16560 | LSB Step Error           | 8V Range, FV-Mode = 1, Post auto calibration                                                |     | 124 |     | μV    |

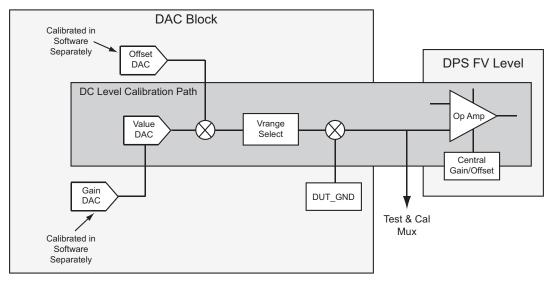

There are 3 on-chip internal DACs used for:

- 1. DC Level

- 2. DC Level Offset Correction

- 3. DC Level Gain Correction

DAC testing is performed post DAC Cal Bit Calibration.

#### **DC Electrical Specifications - DAC**

VOH\_SDIO = VDD, V\_REF = +3V, DUT\_GND = 0V. Parameters with MIN and/or MAX limits are 100% tested at TA = +25°C, unless otherwise specified. Temperature limits established by characterization and are not production tested.

| SPEC#    | PARAMETER          | TEST CONDITIONS                                                                                                           | MIN  | TYP  | MAX  | UNITS     |

|----------|--------------------|---------------------------------------------------------------------------------------------------------------------------|------|------|------|-----------|

| LEVEL DA | AC TEST            | ·                                                                                                                         |      |      |      |           |

| 16100    | Span               | Offset and Gain DACs both programmed to mid scale (Code 7FFF),<br>Span = DAC(FFFF) - DAC(0000), Notes 1, 2                | 7.5  | 8.9  | 9.5  | V         |

| 16110    | Linearity Error    | Offset and Gain DACs both programmed to mid scale (Code 7FFF), Notes 1, 2, 3                                              | -2   | 0.6  | +2   | mV        |

| 16120    | Bit Test Error     | Offset and Gain DACs both programmed to mid scale (Code 7FFF), Notes 1, 2, 4                                              | -2   | 0.6  | +2   | mV        |

| 16190    | Droop Test         | Notes 1, 5                                                                                                                | -1   |      | +1   | mV/ms     |

| 16400    | DAC Noise          | FV = 0V, Measured at FORCE_0, RMS measurement, Note 1                                                                     |      |      | +1.0 | m۷        |

| OFFSET D | DAC TEST           | ·                                                                                                                         |      |      |      |           |

| 16200    | + Adjustment Range | Level and Gain DACs both programmed to mid scale (Code 7FFF),<br>Code 0000, FFFF relative to mid scale (7FFF), Notes 1, 2 | +4.5 | +5.4 | +6.6 | % of Span |

| 16210    | - Adjustment Range | Level and Gain DACs both programmed to mid scale (Code 7FFF),<br>Code 0000, FFFF relative to mid scale (7FFF), Notes 1, 2 | -6.6 | -5.4 | +4.5 | % of Span |

| 16220    | Linearity Error    | Level and Gain DACs both programmed to mid scale (Code 7FFF),<br>Notes 1, 2, 3                                            | -3   | 1.5  | +2   | mV        |

| 16230    | Bit Test Error     | Level and Gain DACs both programmed to mid scale (Code 7FFF),<br>Notes 1, 2, 4                                            | -3   | 1.5  | +2   | mV        |

| GAIN DAG | CTEST              | ·                                                                                                                         | •    | •    |      |           |

| 16300    | + Adjustment Range | Level DAC = FFFF, Offset DAC = 7FFF, Code 0000, FFFF relative to mid scale (7FFF), Notes 2, 6                             | 1.18 | 1.25 | 1.30 | V/V       |

| 16300    | - Adjustment Range | Level DAC = FFFF, Offset DAC = 7FFF, Code 0000, FFFF relative to mid scale (7FFF), Notes 2, 6                             | 0.7  | 0.75 | 0.81 | V/V       |

| 16310    | Linearity Error    | Level DAC = FFFF, Offset DAC = 7FFF, Notes 2, 3, 6                                                                        | -3   | 0.5  | +4   | mV/V      |

| 16320    | Bit Test Error     | Level DAC = FFFF, Offset DAC = 7FFF, Notes 2, 4, 6                                                                        | -3   | 0.5  | +4   | mV/V      |

| 16330    | DUT_GND Error      | DUT_GND forced to ±1V. Measured at the FORCE pin, Note 6                                                                  | -6   |      | +6   | m۷        |

#### NOTES:

- 1. VCC = +12V, VCCO\_# = +4V, VEE = -4V, VDD = +3.3V

- 2. DAC tests performed using the DPS in FV mode and the MONITOR output. 8V Range, FV-Mode = 1.

- 3. Linearity Test 17 equal spaced codes relative to a straight line determined by 1/8 and 7/8 measurement points: 0000, 0FFF, 1FFF, 2FFF, 3FFF, 4FFF, 5FFF, 6FFF, 7FFF, 8FFF, 9FFF, 8FFF, 9FFF, 8FFF, 9FFF, 9FFF

- 4. Bit Test Walking 1 and walking 0 to determine the correct bit weight 1's: 8000, 4000, 2000, 1000, 0800, 0400, 0200, 0100, 0080, 0040, 0002, 0010, 0008, 0004, 0002, 00010's: 7FFF, BFFF, DFFF, EFFF, FFFF, FF

- 5. CPU CK turned off. 66ms delay between measurements. Each DC level on the chip checked one at a time.

- 6. VCC = +12.9V,  $VCCO_# = +4V$ , VEE = -2.9V, VDD = +3.2V.

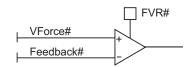

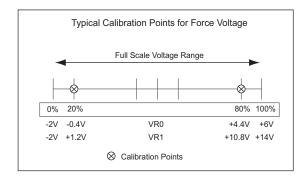

## **Force Voltage**

3. Measure the voltage at FORCE\_#.

**Channel Configuration:**

1. Feedback# = SENSE\_#

The sequence of events performed for FV Testing is:

- 1. Program VF#

- 2. Force current at FORCE\_# w/external resource

#### **DC Electrical Specifications - FV**

Parameters with MIN and/or MAX limits are 100% tested at TA = +25 °C, unless otherwise specified. Temperature limits established by characterization and are not production tested.

| Spec #    | PARAMETER             | TEST CONDITIONS                                                                                                                                                                                                                                                                                                            | MIN | TYP       | MAX | UNITS |

|-----------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------|-----|-------|

| FV (POST  | CALIBRATION)          |                                                                                                                                                                                                                                                                                                                            |     | 1         |     |       |

| 14200     | Output Force Error    | VCC =+ 12.5V, VCCO_# = +4V, VEE = -3.5V, VDD = +3.45V, VOH_SDIO = VDD, VREF = +3V, DUT_GND = OV, FV_MODE = 0 (8V range), Calibration points: 0V, 2.5V No-Load Test Points: -1.5V, +1V, +3.75V. Tested in IR3, IR4, and IR5 only. Full-Load Test Points (±I <sub>MAX</sub> ): OV, 3V. Tested in IR3, IR4, and IR5 only.     | -5  |           | +5  | mV    |

| 14201     | Output Force Error    | VCC =+ 12.5V, VCCO_# = +4V, VEE = -3.5V, VDD = +3.45V, VOH_SDIO = VDD, VREF = +3V, DUT_GND = OV, FV_MODE = 1 (16V range), Calibration points: 0V, 10V No-Load Test Points: -2V, +5V, +12V. Tested in IRO and IR4 only. Full-Load Test Points (±I <sub>MAX</sub> ): -1.5V, 11V. Tested in IRO, IR1, IR2, IR3, and IR4 only. | -10 | A         | +10 | mV    |

| FV TEMPE  | RATURE COEFFICIENT    | ·                                                                                                                                                                                                                                                                                                                          |     |           |     |       |

|           | 8V Range              | VCC = +13V, VCCO_# = +4V, VEE = -3V,<br>VDD = +3.3V, VOH_SDIO = VDD, V_REF = +3V, DUT_GND = 0                                                                                                                                                                                                                              |     | 60        |     | μV/°C |

|           | 16V Range             | VCC = +13V, VCCO_# = +4V, VEE = -3V,<br>VDD = +3.3V, VOH_SDIO = VDD, V_REF = +3V, DUT_GND = 0                                                                                                                                                                                                                              |     | 200       |     | μV/°C |

| HIZ LEAKA | AGE                   |                                                                                                                                                                                                                                                                                                                            |     |           |     |       |

| 14090     | FORCE_#, SENSE_#      | VCC = +12.5V, VCCO_# = +4V, VEE = -3.5V,<br>VDD = +3.45V, VOH_SDIO = VDD, V_REF = +3V, DUT_GND =<br>0, Tested at 0V, (VCC-1.5V), VEE, TightLoop*# = 1                                                                                                                                                                      | -5  | < 0.1     | +5  | nA    |

| CAPACITA  | NCE                   |                                                                                                                                                                                                                                                                                                                            |     |           |     |       |

|           | FORCE_# Capacitance   | VCC = +12.5V, VCCO_# = +4V, VEE = -3.5V, VDD = +3.25V,<br>VOH_SDIO = VDD, V_REF = +3V, DUT_GND = 0                                                                                                                                                                                                                         |     | 400       |     | pF    |

|           | SENSE_# Capacitance   | VCC = +12.5V, VCCO_# = +4V, VEE = -3.5V, VDD = +3.25V,<br>VOH_SDIO = VDD, V_REF = +3V, DUT_GND = 0                                                                                                                                                                                                                         |     | 15        |     | pF    |

| PROTECTIO | ON                    |                                                                                                                                                                                                                                                                                                                            |     | 1         | 1   |       |

|           | Short Circuit Current | VCC = +12.5V, VCCO_# = +4V, VEE = -3.5V, VDD = +3.25V,<br>VOH_SDIO = VDD, V_REF = +3V, DUT_GND = 0, IR5,<br>FV-Mode = 0, FV = +3V, output shorted to ground                                                                                                                                                                |     | 768 ± 20% |     | mA    |

## **Measure Current**

Post CME Adjust.

#### **TABLE 1. OUTPUT SOURCING**

| RANGE                                                                                              | CAL POINTS       | TPI                          | TPI2  |

|----------------------------------------------------------------------------------------------------|------------------|------------------------------|-------|

|                                                                                                    |                  |                              |       |

| IR0                                                                                                | +5V/0.8 • Imax   | +5V/+I <sub>MAX</sub>        | +5V/0 |

| FV-Mode = 1                                                                                        | +5V/0.2 • Imax   | +5V/(+I <sub>MAX</sub> /2)   |       |

| VCC = +12.5V, VCCO_# = +4V, VEE = -3.5V, VDD = +3.25V,<br>VOH_SDIO = VDD, V_REF = +3V, DUT_GND = 0 |                  |                              |       |

| IR1 - IR4                                                                                          | +5V/0.8 • Imax   | +5V/+I <sub>MAX</sub>        |       |

| FV-Mode = 1                                                                                        | +5V/0.2 • Imax   | +5V/(+I <sub>MAX</sub> /2)   |       |

| VCC = +12.5V, VCCO_# = +4V, VEE = -3.5V, VDD = +3.25V,<br>VOH_SDIO = VDD, V_REF = +3V, DUT_GND = 0 |                  | +5V/0                        |       |

| IR3 - IR5                                                                                          | +2.5V/0.8 • Imax | +2.5V/+I <sub>MAX</sub>      |       |

| FV-Mode = 0                                                                                        | +2.5V/0.2 • Imax | +2.5V/(+I <sub>MAX</sub> /2) |       |

| VCC = +8V, VCCO_# = +4V, VEE = -3.5V, VDD = +3.25V, VOH_SDIO = VDD, V_REF = +3V, DUT_GND = 0       | ENI              | +2.5V/0                      |       |

#### TABLE 2. OUTPUT SINKING

| RANGE                                                                                              | CAL POINTS                  | TPI                        |

|----------------------------------------------------------------------------------------------------|-----------------------------|----------------------------|

| IRO – IR4                                                                                          | +5V/-0.2 • Imax             | +5V/-I <sub>MAX</sub>      |

| FV-Mode = 1                                                                                        | +5V/-0.8 • I <sub>MAX</sub> | +5V/(-I <sub>MAX</sub> /2) |

| VCC = +12.5V, VCCO_# = +4V, VEE = -3.5V, VDD = +3.25V,<br>VOH_SDIO = VDD, V_REF = +3V, DUT_GND = 0 |                             | +5V/0                      |

| IR3 - IR5                                                                                          | +2.5V/-0.2 • Imax           | +2.5V/-I <sub>MAX</sub>    |

| FV-Mode = 0                                                                                        | +2.5V/-0.8 • Imax           | +2.5V/(-Imax/2)            |

| VCC = +8V, VCCO_# = +4V, VEE = -3.5V,<br>VDD = +3.25V, VOH_SDIO = VDD,<br>V_REF = +3V, DUT_GND = 0 |                             | +2.5V/0                    |

# **DC Electrical Specifications – Measure Current**

Parameters with MIN and/or MAX limits are 100% tested at TA = +25°C, unless otherwise specified. Temperature limits established by characterization and are not production tested.

| Spec #    | PARAMETER                       | TEST CONDITIONS                                                                                      | MIN                 | TYP    | MAX                 | UNITS                |

|-----------|---------------------------------|------------------------------------------------------------------------------------------------------|---------------------|--------|---------------------|----------------------|

| FII and M | (POST CALIBRATION)              |                                                                                                      |                     |        |                     |                      |

| 14100A    | Measure Current Error           | TPI (See Tables 1 and 2), IRO,<br>Bbias = 0, FV_MODE = 1                                             | -0.1% FS            |        | +0.1% FS            | nA                   |

| 14100B    | Measure Current Error           | TPI2 (See Tables 1 and 2), IRO,<br>Bbias = 0, FV_MODE = 1                                            | -0.3% FS            |        | +0.3% FS            | nA                   |

| 14101     | Measure Current Error           | TPI (See Tables 1 and 2), IR1,<br>Bbias = 0, FV_MODE = 1                                             | -(0.1% FS + 0.1%MV) |        | +(0.1% FS + 0.1%MV) | nA                   |

| 14102     | Measure Current Error           | TPI (See Tables 1 and 2), IR2,<br>Bbias = 0, FV_MODE = 1                                             | -(0.1% FS + 0.1%MV) |        | +(0.1% FS + 0.1%MV) | μΑ                   |

| 14103A    | Measure Current Error           | TPI (See Tables 1 and 2), IR3,<br>Bbias = 1, IOUT > ±256µA, FV_MODE = 1                              | -(0.1% FS + 0.1%MV) |        | +(0.1% FS + 0.1%MV) | μΑ                   |

| 14103B    | Measure Current Error           | TPI (See Tables 1 and 2), IR3,<br>Bbias = 1, -256μA ≤ IOUT ≤ 256μA,<br>FV_MODE = 0                   | -1.25% FS           |        | +1.25%FS            | μΑ                   |

| 14104     | Measure Current Error           | TPI (See Tables 1 and 2), IR4,<br>Bbias = 1, IOUT > ±2.56mA, FV_MODE = 1                             | -(0.1% FS + 0.1%MV) |        | +(0.1% FS + 0.1%MV) | μΑ                   |

| 14104B    | Measure Current Error           | TPI (See Tables 1 and 2), IR4,<br>Bbias = 1, -2.56mA ≤ IOUT ≤2.56mA,<br>FV_MODE = 0                  | -1.25% FS           |        | +1.25%FS            | mA                   |

| 14105     | Measure Current Error           | TPI (See Tables 1 and 2), IR5,<br>Bbias = 1, IOUT > ±25.6mA, FV_MODE = 0                             | -(0.1% FS + 0.1%MV) |        | +(0.1% FS + 0.1%MV) | mA                   |

| 14105B    | Measure Current Error           | TPI (See Tables 1 and 2), IR5,<br>Bbias = 1, -25.6mA ≤ IOUT ≤ 25.6mA,<br>FV_MODE = 0                 | -1.25% FS           |        | +1.25%FS            | mA                   |

|           | MI Temperature Coefficient      | IR0                                                                                                  |                     | ±0.025 |                     | nA/°C                |

|           | MI Temperature Coefficient      | IR1                                                                                                  |                     | ±0.335 |                     | nA/°C                |

|           | MI Temperature Coefficient      | IR2                                                                                                  |                     | ±1     |                     | nA/°C                |

|           | MI Temperature Coefficient      | IR3                                                                                                  |                     | ±0.340 |                     | μ <b>A</b> /°C       |

|           | MI Temperature Coefficient      | IR4                                                                                                  |                     | ±2.03  |                     | μA/°C                |

|           | MI Temperature Coefficient      | IR5                                                                                                  |                     | ±4.18  |                     | μA/°C                |

| Common    | Mode Error (CME)                |                                                                                                      | 1                   | 1      |                     | 1                    |

| 14140     | Maximum CME Adjustment<br>Range | VCC = +12.9V, VCCO_# =+ 4V, VEE =<br>-2.9V, VDD = +3.2V, VOH_SDIO =<br>VDD, VREF = +3V, DUT_GND = 0V | -0.0125             |        | +0.0125             | %FS<br>Current/<br>V |

## **Force Current**

Post CME Adjust.

#### **TABLE 3. OUTPUT SOURCING**

|                                                                                                    | CAL POINTS                            | TPI                                                          |

|----------------------------------------------------------------------------------------------------|---------------------------------------|--------------------------------------------------------------|

| IRO – IR4                                                                                          | +5V/0.6 • Imax                        | +5V/+I <sub>MAX</sub>                                        |

| FV-Mode = 1                                                                                        | +5V/-0.6 • Imax                       | +5V/(+I <sub>MAX</sub> /2)<br>+5V/(+I <sub>MAX</sub> /5)     |

| VCC = +12.5V, VCCO_# = +4V, VEE = -3.5V, VDD = +3.25V, VOH_SDIO = VDD, V_REF<br>= +3V, DUT_GND = 0 |                                       | +5V/(+I <sub>MAX</sub> /10)                                  |

| IR3 – IR5                                                                                          | RANGE                                 | +2.5V/+I <sub>MAX</sub>                                      |

| FV-Mode = 0                                                                                        | +2.5V/0.6 • Imax<br>+2.5V/-0.6 • Imax | +2.5V/(+I <sub>MAX</sub> /2)<br>+2.5V/(+I <sub>MAX</sub> /5) |

| VCC = +8V, VCCO_# = +4V, VEE = -3.5V, VDD = +3.25V, VOH_SDIO = VDD, V_REF = +3V, DUT_GND = 0       |                                       | +2.5V/(+I <sub>MAX</sub> /10)                                |

#### TABLE 4. OUTPUT SINKING

| RANGE                                                                                              | CAL POINTS                  | TPI                                                          |

|----------------------------------------------------------------------------------------------------|-----------------------------|--------------------------------------------------------------|

| IR0 - IR4                                                                                          | +5V/0.6 • Imax              | +5V/-I <sub>MAX</sub>                                        |

| FV-Mode = 1                                                                                        | +5V/-0.6 • I <sub>MAX</sub> | +5V/(-I <sub>MAX</sub> /2)<br>+5V/(-I <sub>MAX</sub> /5)     |

| VCC = +12.5V, VCCO_# = +4V, VEE = -3.5V, VDD = +3.25V, VOH_SDIO = VDD,<br>V_REF = +3V, DUT_GND = 0 |                             | +5V/(-I <sub>MAX</sub> /10)                                  |

| IR3 – IR5                                                                                          | +2.5V/0.6 • Imax            | +2.5V/-I <sub>MAX</sub>                                      |

| FV-Mode = 0                                                                                        | +2.5V/-0.6 • Imax           | +2.5V/(-I <sub>MAX</sub> /2)<br>+2.5V/(-I <sub>MAX</sub> /5) |

| VCC = +8V, VCCO_# = +4V, VEE = -3.5V,<br>VDD = +3.25V, VOH_SDIO = VDD,<br>V_REF = +3V, DUT_GND = 0 |                             | +2.5V/(-I <sub>MAX</sub> /10)                                |

## **DC Electrical Specifications – Force Current**

Parameters with MIN and/or MAX limits are 100% tested at TA = +25 °C, unless otherwise specified. Temperature limits established by characterization and are not production tested.

| Spec #    | PARAMETER                       | TEST CONDITIONS                                                                                         | MIN     | TYP   | MAX     | UNITS                |

|-----------|---------------------------------|---------------------------------------------------------------------------------------------------------|---------|-------|---------|----------------------|

| FII and M | (POST CALIBRATION)              |                                                                                                         | '       | '     |         | •                    |

| 15100     | Force Current Error             | TPI (See Tables 3 and 4), IRO,<br>Bbias = 0                                                             | -100    |       | +100    | nA                   |

| 15101     | Force Current Error             | TPI (See Tables 3 and 4), IR1,<br>Bbias = 0                                                             | -1      |       | +1      | μА                   |

| 15102     | Force Current Error             | TPI (See Tables 3 and 4), IR2,<br>Bbias = 0                                                             | -10     |       | +10     | μА                   |

| 15103     | Force Current Error             | TPI (See Tables 3 and 4), IR3,<br>Bbias = 0                                                             | -200    |       | +200    | μА                   |

| 15104     | Force Current Error             | TPI (See Tables 3 and 4), IR4,<br>Bbias = 0                                                             | -1      |       | +1      | mA                   |

| 15105     | Force Current Error             | TPI (See Tables 3 and 4), IR5,<br>Bbias = 0                                                             | -10     |       | +10     | mA                   |

|           | FI Temperature Coefficient      | IR0                                                                                                     |         | ±1.9  |         | nA/°C                |

|           | FI Temperature Coefficient      | IR1                                                                                                     |         | ±1.6  |         | nA/°C                |

|           | FI Temperature Coefficient      | IR2                                                                                                     |         | ±7.7  |         | nA/°C                |

|           | FI Temperature Coefficient      | IR3                                                                                                     |         | ±21.3 |         | μA/°C                |

|           | FI Temperature Coefficient      | IR4                                                                                                     |         | ±1    |         | μA/°C                |

|           | FI Temperature Coefficient      | IR5                                                                                                     |         | ±19.5 |         | μA/°C                |

| Common    | Mode Error (CME)                |                                                                                                         |         |       |         |                      |

| 15140     | Maximum CME Adjustment<br>Range | VCC = +12.9V, VCCO_# =+ 4V,<br>VEE = -2.9V, VDD = +3.2V,<br>VOH_SDIO = VDD, VREF = +3V,<br>DUT_GND = 0V | -0.0125 |       | +0.0125 | %FS<br>Current/<br>V |

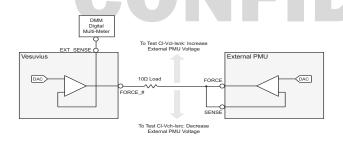

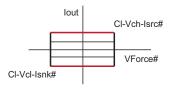

#### **Current Clamps**

Current clamps are tested in IR5 only.

The sequence of events to test the Source Current Clamps is as follows (this list is not an all-inclusive setup list). Please also refer to the figure below:

- 1. Program CI-Vch-Isrc<15:0> to Test Point/Calibration Point.

- 2. Set Cl-En# = 1.

- 3. Set proper path to so that: Feedback# = Force\_#.

- 4. Set Con-ES-F# = 1.

- 5. Set ForceA#<15:0> = 2V.

- 6. Measure Voltage at EXT SENSE pin. (Initial FV Level)

- 7. Connect  $\mathbf{10}\Omega$  load from FORCE\_# on Vesuvius to External PMII

- 8. Set External PMU voltage = 2V.

- Decrease External PMU voltage until voltage measured at EXT\_SENSE moves from the initial FV Level by the following amount: 15mV> (Initial FV Level - Measured FV Level) >5mV.

- 10. Use External PMU to measure current sourced by Vesuvius.

The sequence of events to test the Sink Current Clamps is as follows (this list is not an all-inclusive setup list). Please also refer to the figure below:

- 1. Program Cl-Vcl-Snk#<15:0> to Test Point/Calibration Point.

- 2. Set Cl-En# = 1.

- 3. Set proper path to so that: Feedback# = Force\_#.

- 4. Set Con-ES-F# = 1.

- 5. Set ForceA#<15:0> = 2V.

- 6. Measure Voltage at EXT\_SENSE pin. (Initial FV Level)

- 7. Connect  $\mathbf{10}\Omega$  load from FORCE\_# on Vesuvius to External PMU.

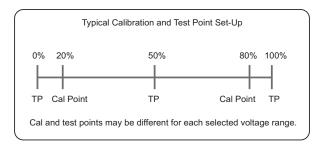

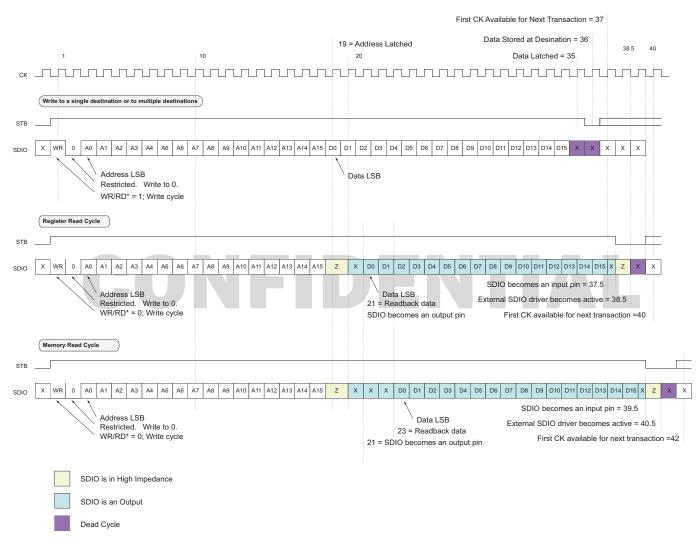

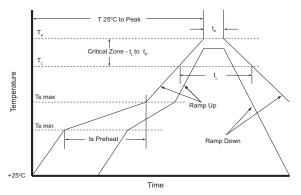

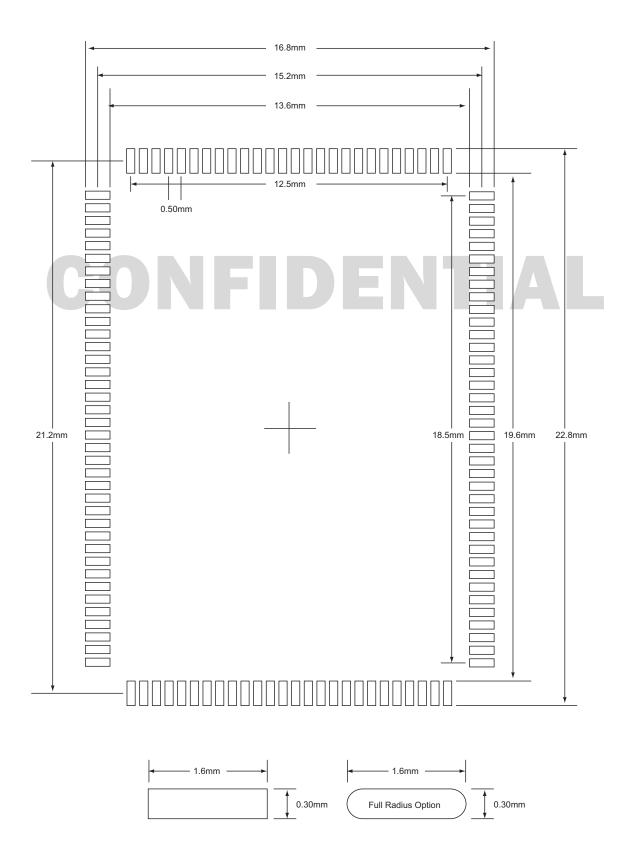

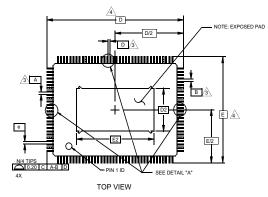

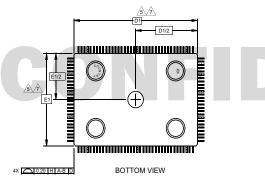

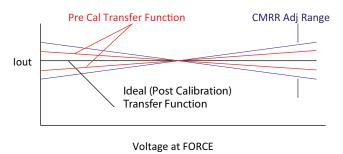

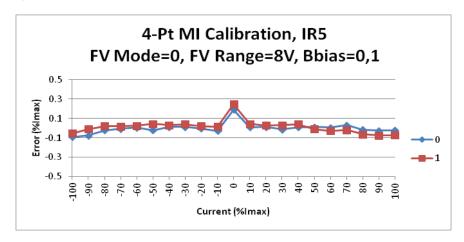

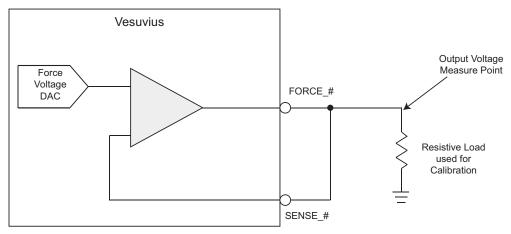

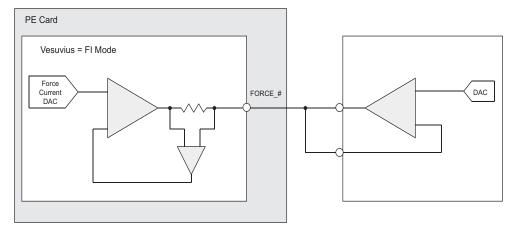

- 8. Set External PMU voltage = 2V.