# **ISL55185 EVM Getting Started**

**Rev A02: In Progress**

This document contains information on a product under development. The parametric information contains target parameters that are subject to change.

### **Table of Contents**

| 1 Inti  | roduction                                                | 4  |

|---------|----------------------------------------------------------|----|

| 1.1     | Unpacking - ISL55185 EVM Contents                        |    |

| 1.2     | Recommended Test and Measurement Setup                   |    |

| 1.2     |                                                          |    |

| 1.2.    | 11 7                                                     |    |

| 1.2.    | 3 Test Equipment                                         | 5  |

| 1.3     | Software Installation                                    |    |

| 1.3.    |                                                          |    |

| 1.3.    | ,                                                        |    |

| 1.3.    |                                                          |    |

| 1.3.    | 8                                                        |    |

| 1.3.    |                                                          |    |

| 2 Get   | ting Started                                             |    |

| 2.1     | Quick Start Instructions                                 | 7  |

| 2.2     | Default Configuration Setup Options                      | 8  |

| 2.2.    | 1 PMU Force Voltage and Active Load                      | 8  |

| 2.3     | ISL55185 EVM Jumper Definitions                          | 9  |

| 2.4     | Motherboard Jumper and SMA Definition                    | 9  |

| 2.5     | ISL55185 EVM Menu Dialog Boxes                           |    |

|         | tailed Hardware Description                              |    |

|         | •                                                        |    |

| 3.1     | ISL55185 EVM Loadboard Detailed Description              |    |

| 3.2     | Capacitor and Resistor Network Definitions               | 14 |

| 3.3     | ADC and Analog Mux                                       | 15 |

| 3.4     | ISL55185 EVM Loadboard Controller                        | 16 |

| 4 Doc   | cument Revision History                                  | 17 |

|         | ·                                                        |    |

|         | f Figures                                                |    |

|         | 1: Installation Directory Structure                      |    |

|         | 2: Expected Current Readings                             |    |

|         | 3: PMU FV Block Diagram4: Device Config Menu Options     |    |

|         | 5: Elevate Semiconductor EVM Overview Block Diagram      |    |

|         | 5: ISL55185 EVM Loadboard Detailed Block Diagram         |    |

|         | 7: ISL55185 EVM Capacitor/Resistor Network Block Diagram |    |

|         | 3: Controller Section Detailed Block Diagram             |    |

|         | _                                                        |    |

|         | f Tables                                                 |    |

|         | : ISL55185 EVM Contents                                  |    |

|         | : Power Supply Requirements                              |    |

|         | : ISL55185 Default Configuration Options                 |    |

| Table 4 | : ISL55185 EVM Jumper Definitions                        | 9  |

|         | : TC# Resource Allocation                                |    |

| able 6  | : Capacitor Network Definitions                          | 14 |

| Table 7: ISL55185 EVM Resistor Network Definitions                       | 14 |

|--------------------------------------------------------------------------|----|

| Table 8: FVMI Analog Mux – VINPOS(A) & VINNEG(A) Mapping                 | 15 |

| Table 9: ISL55185 EVM Loadboard Analog Mux Definitions – LB AMUX Mapping |    |

#### 1 Introduction

Congratulations on your purchase of a Elevate Semiconductor ISL55185 EVM evaluation system. You will find that it serves as an invaluable development platform to help get your product to market in the shortest possible time. The ISL55185 EVM and Graphical User Interface (GUI) allow the customer to demonstrate and evaluate the ISL55185 performance and functionality.

This document provides the instructions to install, setup, and operate the ISL55185 EVM. Refer to the *Elevate Semiconductor EVM User's Guide* for a detailed description of the FVMI and Motherboard.

#### 1.1 Unpacking - ISL55185 EVM Contents

Please check the contents of the ISL55185 EVM shipping carton to make sure you have received all of the items listed in Table 1. The system is already configured for the best setup, except for connections to the power supply, PC controller, and test equipment.

Table 1: ISL55185 EVM Contents

| Qty   | Description                                                      |  |

|-------|------------------------------------------------------------------|--|

| 1 ea. | ISL55185 EVM System (3 boards: Loadboard, EVM Motherboard, Octal |  |

|       | FVMI)                                                            |  |

| 1 ea. | ISL55185 EVM Getting Started (this document)                     |  |

| 1 ea. | Elevate Semiconductor User Interface Program Installation CD     |  |

| 1 ea. | DB25M-DB25M, 6 Foot Parallel Port Cable                          |  |

### 1.2 Recommended Test and Measurement Setup

#### 1.2.1 Power Supply

Table 2 provides the required power supplies and current rating. The power supplies are connected using standard banana plugs. The customer needs to provide the power supply cables.

It is recommended to use a triple supply to control the EVM supplies. This allows the 3 EVM supplies to be turned on at the same time. However, if this is not feasible, then the supplies should be enabled in the following sequence. Power down should be performed in the reverse order.

- 1. +20V

- 2. -15V

- 3. +5V

The ISL55185 VCC and VEE are gated using an Opto-FET switch on the loadboard so it is safe to set and enable the ISL55185 VCC/VEE voltages before powering up the EVM and running the software.

**Table 2: Power Supply Requirements**

| Module           | Supply                | Current Rating |

|------------------|-----------------------|----------------|

| EVM              | +20V (1)              | 1.0 A          |

| EVM              | +5V                   | 0.5 A          |

| EVM              | -15V                  | 0.5 A          |

| ISL55185 VCC (4) | +10V (2, 3)           | 0.5 A          |

| ISL55185 VEE (4) | -5V <sup>(2, 3)</sup> | 0.5 A          |

- 1) The EVM +20V could also be used as the ISL55185 VCC

- The ISL55185 VCC VEE voltage should not exceed 32V. Refer to the ABS max section in the datasheet.

- Once the EVM operation is verified, the customer can adjust the VCC/VEE supplies.

- 4) There is a provision to use the FVMI LT1206 to source the VCC/VEE supplies; this is controlled by the E2/E3 Jumpers on the loadboard. The LT1206 can support +15V/-10V. The EVM GUI software V3.9.x does not support the option where the FVMI LT1206 is used to source the VCC/VEE supplies so an external power supply must be used.

#### 1.2.2 PC Controller

To use the ISL55185 EVM User Interface Program (UIP), a PC with the following configuration is required:

- Win98, Win2000, WinNT 4.0+, or Win XP

- Parallel/Printer Port 25-pin female connector

#### 1.2.3 Test Equipment

- Voltage and/or Current Meter

- Voltage and/or Current Source

#### 1.3 Software Installation

There are 2 steps to install the ISL55185 EVM demonstration program.

- 1. Install the ISL55185 EVM UIP from the CD-ROM.

- 2. Install the parallel port driver (ParPort2k).

Figure 1 illustrates the default directory structure. The user may change the <root dir> during the installation.

#### Figure 1: Installation Directory Structure

<Root Dir>\Planet ATE\EVM\EVM GUI

\Documents

\ParPort2k

#### 1.3.1 ISL55185 EVM UIP Installation

To install the ISL55185 EVM software package, run the SETUP program on the distribution CD and follow the prompts. The **PlanetATE.exe** executable will be installed in the **EVM GUI** sub-directory. In addition, a short cut will be installed onto the desktop and in the **Start->Programs** folder. The **Start->Programs** folder also contains links to the different product datasheets, EVM User's Guide, and documentation folder.

#### 1.3.2 Parallel Port (ParPort2K) Installation

To install the ParPort2K parallel port driver, run the **setup.exe** from the **ParPort2k** sub-directory after the main installation is complete and click the **Install** button. For WinNT users, the user must have administration rights.

Note: ParPort2k is a copyright of Zeecube Software.

#### 1.3.3 Reboot Machine

After the ISL55185 EVM and Parallel Port software is installed, it is recommended to re-boot the machine.

#### 1.3.4 Launching the Elevate Semiconductor Program

The user can launch the Elevate Semiconductor GUI from the desktop, **Start->Programs** folder, or **EVM GUI** sub-directory.

#### 1.3.5 Software Un-Installation

The Elevate Semiconductor demonstration program may be un-installed using the **Add/Remove Program** from the Windows Control Panel.

### 2 Getting Started

The ISL55185 EVM is shipped in a pre-configured state that allows a customer to evaluate the different modes.

Note: Any external equipment providing digital signals into the ISL55185 device should only be enabled after the ISL55185 EVM is enabled. Also, the external equipment should be disabled prior to disabling the ISL55185 EVM.

#### 2.1 Quick Start Instructions

- 1. Disable external power supplies

- 2. Connect the power supplies cables (not provided) from the power supply to the Elevate Semiconductor EVM Motherboard and ISL55185 loadboard; refer to Section 2.2.1.

- 3. Connect the parallel cable (provided) from the PC to J2 on the Octal FVMI board.

- 4. Connect the EVM to any external equipment; refer to Section 2.2.

- 5. Setup Motherboard Jumpers; refer to Section 2.4

- 6. Set external power supply voltages and current.

- 7. Enable external power supply.

- 8. Run the Elevate Semiconductor GUI software; refer to Section 1.3.4 for details.

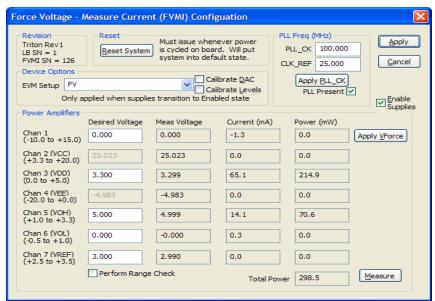

- 9. At the Force Voltage Measure Current dialog box (refer to Figure 2 below):

- a. Select the **EVM Setup** option based on the desired configuration, see Section 2.2

- b. Select the **Enable Supplies** check box

- c. Hit the **Apply** button to power up the device.

- 10. At this point, the device should be outputting the desired signal.

Note: the software can measure the external VCC/VEE supply voltage but has no mechanism to measure the external VCC/VEE supply current.

Figure 2: Expected Current Readings

The **Reset System** will put the EVM and ISL55185 device into the default state. The **Reset System** should be issued whenever the power supply is powered OFF then ON. The **Reset System** is automatically performed when the program is initially launched.

### 2.2 Default Configuration Setup Options

The EVM has several default options for configuring for device into different modes.

**Table 3: ISL55185 Default Configuration Options**

| Mode                 | See Section # | Brief Description                                        |

|----------------------|---------------|----------------------------------------------------------|

| Hardware Reset       | N/A           | All registers default to the hardware default state.     |

| Three-State (High-Z) | N/A           | Puts device in three-state (high-Z). Opens all switches. |

| FV (Force Voltage)   | 2.2.1         | Configures all 8 channels to output 3.0V                 |

#### 2.2.1 PMU Force Voltage and Active Load

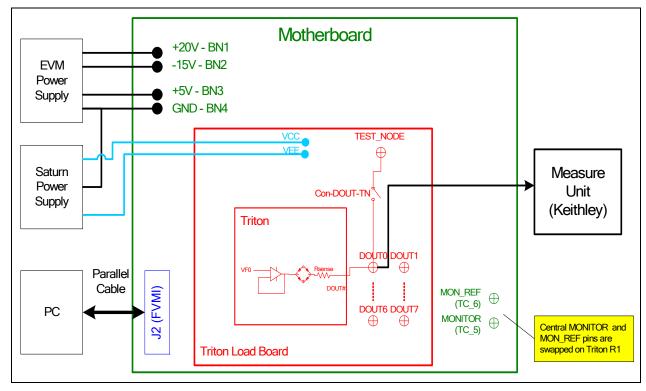

Figure 3 illustrates the recommended configuration for PMU FV and Active Load evaluation. The external measurement unit (MU) should be configured in the opposite mode as ISL55185. After the configuration is completed, use the **DC Levels** dialog box the change the ISL55185 output levels. The user can also connect the DOUT# to TEST\_NODE switch. The TEST\_NODE can be connected to an on-board Resistor Network.

| ISL55185    | MU   |

|-------------|------|

| FVMI        | FIMV |

| Active Load | FVMI |

Figure 3: PMU FV Block Diagram

### 2.3 <u>ISL55185 EVM Jumper Definitions</u>

Table 4 lists the ISL55185 EVM Jumper definitions.

**Table 4: ISL55185 EVM Jumper Definitions**

| Jumper | Description    | Configuration                          |

|--------|----------------|----------------------------------------|

| E1     | Connect VFORCE | Installed                              |

| E2     | VCC Source     | Short Pin 1 & 2. Towards back of board |

| E3     | VEE Source     | Short Pin 1 & 2. Towards back of board |

Note: The EVM GUI software V3.9.x does not support the option where the FVMI LT1206 is used to source the VCC/VEE supplies. An external power supply must be used.

### 2.4 <u>Motherboard Jumper and SMA Definition</u>

Table 5 lists the Tester Channel (TC\_#) connector definitions for the ISL55185 EVM Loadboard.

On the EVM Motherboard, most of the TC\_# signals can be connected to an SMA. In addition, some TC\_# signals (digital inputs) go through a 3-pin jumper to allow the inputs to be sourced from either the SMA or a latch.

**Table 5: TC# Resource Allocation**

| T0#   | Ι                |                | EVALUE.                                                                                      |

|-------|------------------|----------------|----------------------------------------------------------------------------------------------|

| TC#   | Usage            | EVM MB         | EVM MB                                                                                       |

|       | TOUL             | Jumper         | Jumper Configuration                                                                         |

| 1     | TPIN             | -              |                                                                                              |

| 2     | CPU_SDIO         | -              |                                                                                              |

| 3     | CPU_STB          | -              |                                                                                              |

| 4     | RESET            | -              |                                                                                              |

| 5     | MONITOR          | -              |                                                                                              |

| 6     | MON_REF          | -              |                                                                                              |

| 7     | Reserved         | -              |                                                                                              |

| 8     | MON#             | -              |                                                                                              |

| 9     | MON_REF#         | -              |                                                                                              |

| 10    | CPU_CK           | -              |                                                                                              |

| 11*   | EXT_FORCE#_P     | -              |                                                                                              |

| 12*   | EXT_SENSE#_P     | -              |                                                                                              |

| 13    | TJ               | -              |                                                                                              |

| 14*   | LB_AMUX_P        | -              |                                                                                              |

| 15    | DUT_GND          | E20            | Only applicable when DUT_GND_SEL = TC_15                                                     |

|       | DG_[D:A]         |                | Install to short to GND                                                                      |

|       |                  |                | Do not install to use TC_15 SMA                                                              |

| 16    | TEST_IN          | E13            | Only applicable when TEST_IN_SEL = TC_16                                                     |

|       |                  |                | Install to short to GND                                                                      |

|       |                  |                | Do not install to use TC_16 SMA                                                              |

| 17    | DATA0/4          | E3             | Short Pin 1 & 2: source from latch                                                           |

|       |                  |                | Short Pin 2 & 3: source from SMA                                                             |

| 18    | DATA1/5          | E4             | Short Pin 1 & 2: source from latch                                                           |

|       |                  |                | Short Pin 2 & 3: source from SMA                                                             |

| 19    | EN0/4            | E4             | Short Pin 1 & 2: source from latch                                                           |

|       |                  |                | Short Pin 2 & 3: source from SMA                                                             |

| 20    | EN1/5            | E6             | Short Pin 1 & 2: source from latch                                                           |

| - 0.4 | ODL DOL          |                | Short Pin 2 & 3: source from SMA                                                             |

| 21    | SDI_RCK          | E1             | Always Short Pin 1 & 2. towards back of board                                                |

| 22    | DATA2/6          | E7             | Short Pin 1 & 2: source from latch                                                           |

| - 00  | DATA 0/7         | F0             | Short Pin 2 & 3: source from SMA                                                             |

| 23    | DATA3/7          | E8             | Short Pin 1 & 2: source from latch                                                           |

| 24    | ENO/C            | ГО             | Short Pin 2 & 3: source from SMA                                                             |

| 24    | EN2/6            | E9             | Short Pin 1 & 2: source from latch                                                           |

| 25    | EN12/7           | E10            | Short Pin 2 & 3: source from SMA Short Pin 1 & 2: source from latch                          |

| 25    | EN3/7            | =10            | Short Pin 1 & 2: Source from latch Short Pin 2 & 3: source from SMA                          |

| 26    | EXT_MON_SEL0     | E2             | Always Short Pin 1 & 2. towards back of board                                                |

| 27    | EXT_MON_SEL0     | E15            | Always Short Pin 1 & 2. towards back of board  Always Short Pin 1 & 2. towards back of board |

| 28    | EXT_MON_SEL1     | E13            | Always Short Pin 1 & 2. towards back of board  Always Short Pin 1 & 2. towards back of board |

| 29    | Reserved (EVM)   | E14            | Don't care                                                                                   |

| 29    | EXT_MON_OE (ATE) |                | Dont cale                                                                                    |

| 30    | Reserved (EVM)   | E12            | Don't care                                                                                   |

| 30    | EXT_TJ_OE (ATE)  | L12            | Don't baile                                                                                  |

| 31    | Not Used         | <del> </del> - |                                                                                              |

| 32*   | TEST NODE P      | <del> </del> - |                                                                                              |

| JZ    | 1201_140DL_1     |                | <u>J</u>                                                                                     |

Note: An '\*' means the signal goes through a channel protector before routed to TC#.

## 2.5 ISL55185 EVM Menu Dialog Boxes

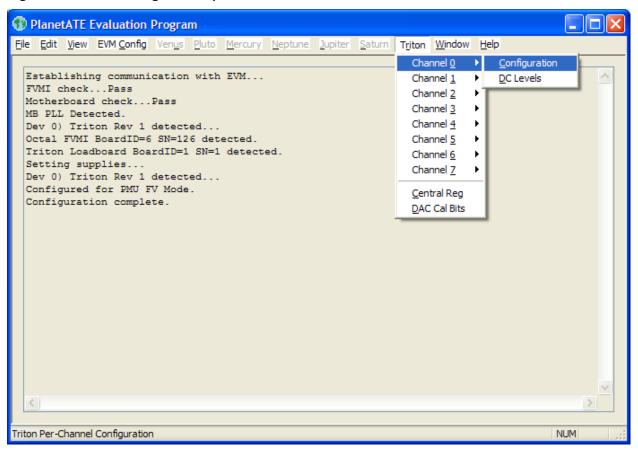

Figure 4 illustrates the ISL55185 EVM menu options. These provide access to the ISL55185 registers.

Figure 4: Device Config Menu Options

### 3 Detailed Hardware Description

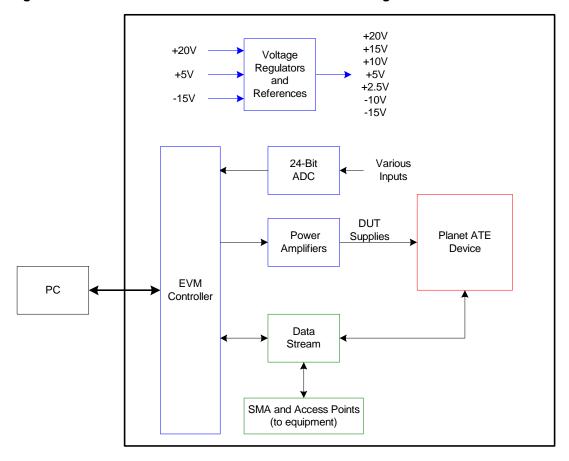

Figure 5 illustrates the ISL55185 EVM system overview. The ISL55185 EVM is comprised of 3 boards:

- Device Loadboard this is the top board and contains the Elevate Semiconductor device. Represented in red in the figure.

- Motherboard this is the middle board and contains the data stream and comparator output test access points. Represented in green in the figure.

- Octal FVMI Board this is the bottom board and contains the power amplifiers, A/D converter, voltage regulators/references, and EVM controller. Represented in blue in the figure.

Refer to the *Elevate Semiconductor EVM User's Guide* document for a detailed description of the Octal FVMI and Motherboard.

Figure 5: Elevate Semiconductor EVM Overview Block Diagram

### 3.1 ISL55185 EVM Loadboard Detailed Description

Figure 6 illustrates the ISL55185 EVM loadboard. Almost all of the circuitry is used to test, validate & characterize on the bench and ATE environment. Besides decoupling caps, the only external component required is the 10K resistor connected to REXT.

Symbol Legend CH2\_FORCE Latch (EVM) or TC\_30 (ATE) EXT\_TJ\_OE (diy 2) Channel Protector LED VCC TC 13 (A/D) ⊕ SMA External Mux Power E3 (diy 2) 2-Pin Jmpr Supply 3-Pin Jmpr VEE TDP Thermal  $\leftarrow$  GND TDN Sensor CH4\_FORCE A/D CH3\_FORCE VDD EXT\_MON\_SEL[3:0] TC 26/27/28 F1 CH1\_FORCE VFORCE EXT\_MON\_OE Latch (EVM) or TC\_29 (ATE) A/D On MB RESET TC\_10/2/3 **←**-3-CK/SDIO/STB MONITOR (A/D) TC 6 MON REF A/D  $(A/\overline{D})$ VREF\_SEL VREF (DPS) On MB VREF TEST NODE REXT\_SEL TEST\_NODE REXT EST\_NODE E20 Rnet DUT\_GND\_SEL . Cload TC\_32 ( DUT\_GND (A/D) **Triton**  $\bigoplus$ DG\_[D:A]\_SEL A/D CON DOUT# TN CON TN DIV2 Mux DG\_[D:A] MB TEST\_IN\_SEL DOUT\_SEL TEST IN E13 VFORCE (controls all 8)  $\oplus$ FORCE\_SEL DOUT# (controls all 8)  $\sqrt{}$ Per-Channel On MB (8x)TC\_11 EXT\_FORCE# (A/D) Parallel DATA[3:0] CHAN\_AMUX Connector Latch TC 12 DATA[3:0] TC17/TC18 (not EXT SENSE# (A/D) TC22/TC23 DATA[7:4] applicable  $\oplus$ On ME Quad on EVM) DIG BANK SEL MB (latch - EVM) (LBDATA3 - ATE) ⊕ On MB EN[3:0] TC\_8 MON# (A/D) Latch TC19/TC20 EN[3:0] CHAN AMUX TC24/TC25 EN[7:4] TC\_9 Quad MON\_REF# (A/D) On MB +5V LPORT3\_IN2 RESET SOT GREEN\_LED On EVMs: (Cbit3) (Cbit1) Start Switch/LEDs TEMP D0 not populated RED LED EEPROM LPORT1[4:2]

Figure 6: ISL55185 EVM Loadboard Detailed Block Diagram

### 3.2 Capacitor and Resistor Network Definitions

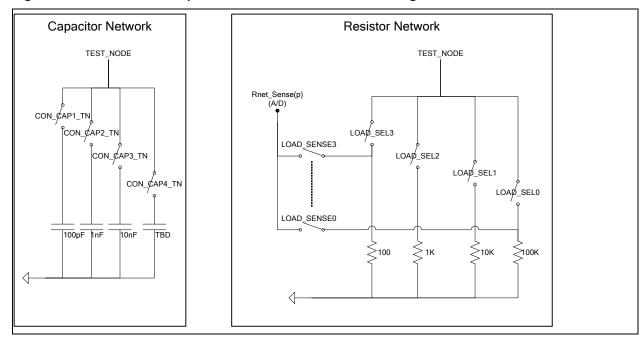

Figure 7 illustrates while Table 6 and Table 7 list the ISL55185 EVM capacitor/resistor load network definitions. Any capacitor combination can be switched in. The software only allows a single resistor value to be switched in.

Figure 7: ISL55185 EVM Capacitor/Resistor Network Block Diagram

**Table 6: Capacitor Network Definitions**

| Code    | Capacitor Value |

|---------|-----------------|

| -1 or 0 | Open All        |

| 1       | 100pF           |

| 2       | 1nF             |

| 4       | 10nF            |

| 8       | TBD             |

**Table 7: ISL55185 EVM Resistor Network Definitions**

| Code | Resistor Value |

|------|----------------|

| -1   | Open All       |

| 0    | 100K           |

| 1    | 10K            |

| 2    | 1K             |

| 3    | 100            |

### 3.3 ADC and Analog Mux

The Octal FVMI contains a 24-bit ADC and analog muxes which allows for the accurate measurement of many device and system voltages. Table 8 lists the ISL55185 EVM loadboard specific mux input sources. Table 9 lists the ISL55185 EVM loadboard AMUX\_OUT analog mux which is routed to the TC-28 and VINN10 nodes.

#### Notes:

- Signals that have a '\_P' appended to the end of the name implies the signal goes through a channel protector or voltage dividers (i.e. VCC) since they could exceed the motherboard supplies (+20V/-15V).

- 2) VINP13 and VINP14 are connected to TC\_31 and TC\_32 on the motherboard.

Table 8: FVMI Analog Mux - VINPOS(A) & VINNEG(A) Mapping

| Addr | VINP#  | VINPOS(A)             | VINN#  | VINNEG(A)             |

|------|--------|-----------------------|--------|-----------------------|

| 7    | VINP8  | Reserved              | VINN8  | VREF                  |

| 8    | VINP9  | MON# (per-chan)       | VINN9  | MON_REF# (per-chan)   |

| 9    | VINP10 | LB_AMUX_P (see below) | VINN10 | LB_AMUX_P (see below) |

| 10   | VINP11 | MONITOR (Central)     | VINN11 | MON_REF (Central)     |

| 11   | VINP12 | REXT                  | VINN12 |                       |

| 12   | VINP13 | TC_31                 | VINN13 |                       |

| 13   | VINP14 | TC_32 (TEST_NODE_P)   | VINN14 |                       |

Table 9: ISL55185 EVM Loadboard Analog Mux Definitions – LB\_AMUX Mapping

| Addr | NO# | LB_AMUX     |

|------|-----|-------------|

| 0    | 1   | DUT_GND     |

| 1    | 2   | DG_A        |

| 2    | 3   | DG_B        |

| 3    | 4   | DG_C        |

| 4    | 5   | DG_D        |

| 5    | 6   | TN_DIV      |

| 6    | 7   | VCC_DIV     |

| 7    | 8   | VEE_DIV     |

| 8    | 9   | EXT_FORCE#  |

| 9    | 10  | EXT_SENSE#  |

| 10   | 11  | TJ          |

| 11   | 12  | TEST_IN     |

| 12   | 13  | SENSE_RNET0 |

| 13   | 14  | SENSE_RNET1 |

| 14   | 15  | SENSE_RNET2 |

| 15   | 16  | SENSE_RNET3 |

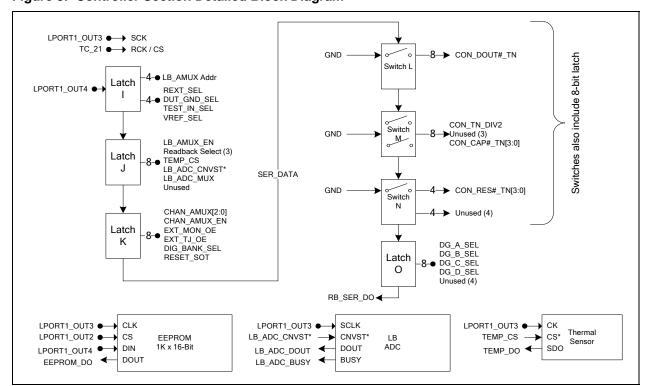

#### 3.4 ISL55185 EVM Loadboard Controller

The ISL55185 EVM loadboard contains seven 8-bit latches (registers), 16K EEPROM, Thermal Sensor, and an Analog-to-Digital Converter (ADC). The Cbit1 to CBit7 are also used to control various relays, the C-Bit# originate from the Octal FVMI board. Figure 8 illustrates the ISL55185 EVM controller section.

The latches are daisy chained together using the SDI\_SCK/RCK/CS signals originating from the Motherboard. The EEPROM is controlled by the LPORT1\_OUT[4:2] signals originating from the motherboard. The loadboard latches are labeled STB\_I to STB\_N. This was named as an extension to the REG\_A to REG\_H Octal FVMI / Motherboard registers.

Note: The EVM GUI software V3.9.x does not support the ability to measure the Loadboard ADC and Thermal Sensor.

Figure 8: Controller Section Detailed Block Diagram

# 4 Document Revision History

| Revision | Date        | Description   |

|----------|-------------|---------------|

| A01      | Feb 7, 2006 | Initial Draft |

| A02      | In Progress |               |